I am forwarding to the 802.3cm reflector a thread discussing MDI lane assignments for 400G-SR8 to encourage broader discussion.

Paul Kolesar

From: Kolesar, Paul

Sent: Wednesday, April 25, 2018 11:55 AM

To: 'Gary Nicholl (gnicholl)' <gnicholl@xxxxxxxxx>; Brian Welch <bwelch@xxxxxxxxxxx>; Chris Cole <chris.cole@xxxxxxxxxxx>; Jeffery Maki <jmaki@xxxxxxxxxxx>; Brian Park <bpark@xxxxxxxxxx>

Cc: Mark Nowell (mnowell) <mnowell@xxxxxxxxx>; Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>; John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>; Tom Palkert <tom.palkert@xxxxxxxxx>; Sommers, Scott <Scott.Sommers@xxxxxxxxx>; Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx; Steve Hanssen <shanssen@xxxxxxxxxx>; David Lai <davlai@xxxxxxxxxx>; Hong Wang <hwang@xxxxxxxxxx>; zshen@xxxxxxxxxx; Rothermel, Brent R <brent.r.rothermel@xxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Gary,

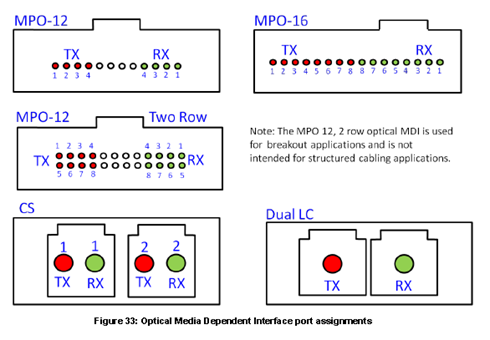

You’ve pointed out two lane assignment options for the 2x12MPO MDI. Here are examples of both for applications that are not lane-number agnostic:

1) for optical engines that are like (2x) SR4, DR4:

T1 T2 T3 T4 o o o o R8 R7 R6 R5

T5 T6 T7 T8 o o o o R4 R3 R2 R1

2) for optical engines that are like SR16:

o o T1 T2 T3 T4 T5 T6 T7 T8 o o

o o R8 R7 R6 R5 R4 R3 R2 R1 o o

where “o” means not used.

Not sure about the MIS advertising issue, but in general if there are options then they should be communicated. It will likely be important, especially for breakout and shuffle

applications.

Paul

From: Gary Nicholl (gnicholl) [mailto:gnicholl@xxxxxxxxx]

Sent: Wednesday, April 25, 2018 9:52 AM

To: Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>; Brian Welch <bwelch@xxxxxxxxxxx>; Chris Cole <chris.cole@xxxxxxxxxxx>; Jeffery

Maki <jmaki@xxxxxxxxxxx>; Brian Park <bpark@xxxxxxxxxx>

Cc: Mark Nowell (mnowell) <mnowell@xxxxxxxxx>; Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>; John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>; Sommers, Scott <Scott.Sommers@xxxxxxxxx>; Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx; Steve Hanssen <shanssen@xxxxxxxxxx>; David Lai <davlai@xxxxxxxxxx>; Hong Wang <hwang@xxxxxxxxxx>;

zshen@xxxxxxxxxx; Rothermel, Brent R <brent.r.rothermel@xxxxxxxxx>

Subject: Re: MPO-24 pin-out definition

Good summary Paul.

As you say it all comes down to whether 802.3cm defines a 2x12MPO MPI for 400G-SR8, and if so whether it goes with the current QSFP-DD lane assignment (which was really only

defined for a 2 x breakout application) or the more traditional lane assignment used by 100G-SR10, etc.

I agree that if the IEEE adopts the later then QSFP-DD, OSFP and COBO need to define an alternative lane assignment for 2xMPO-12.

If we do this then there is nothing to prevent a module from using this alternative mapping for “a

module housing two transceivers (e.g. 2 x SR-4)”.

Does this mean we potentially have to modify the MIS to allow a module to advertise which version of the lane mapping it is using ?

Gary

From: "Kolesar, Paul" <PKOLESAR@xxxxxxxxxxxxx>

Date: Tuesday, April 24, 2018 at 5:01 PM

To: Brian Welch <bwelch@xxxxxxxxxxx>, Chris Cole <chris.cole@xxxxxxxxxxx>, Jeffery Maki <jmaki@xxxxxxxxxxx>, Brian Park <bpark@xxxxxxxxxx>

Cc: Gary Nicholl <gnicholl@xxxxxxxxx>, Mark Nowell <mnowell@xxxxxxxxx>, "Tiger Ninomiya (Takuya)" <Takuya.Ninomiya@xxxxxxxxx>,

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>, Tom Palkert <tom.palkert@xxxxxxxxx>, Scott Sommers <Scott.Sommers@xxxxxxxxx>,

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>, "tommitcheltree@xxxxxxxxxxx" <tommitcheltree@xxxxxxxxxxx>, Steve Hanssen

<shanssen@xxxxxxxxxx>, David Lai <davlai@xxxxxxxxxx>, Hong Wang <hwang@xxxxxxxxxx>, "zshen@xxxxxxxxxx"

<zshen@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Thanks for chiming in. I don’t think there is a difference in how the module form factors are viewed for SM vs MM.

Double density modules can be seen as housing two transceivers, which are broken out before hitting permanent structured

cabling at the patch panel. That’s how the QSFP-DD MSA treats the 2x12MPO interface.

However, the 400G-SR8 PMD is being defined as a 400G interface. And although it will often be used for breakout or

shuffle, it should operate over structured cabling intact. It can do that for Ethernet with either the MPO16 or the 2x12MPO lane assignments of the QSFP-DD because Ethernet is lane-number agnostic. So, at least as far as Ethernet is concerned, the double-module

viewpoint does not seem to provide a reason to choose one MDI over the other.

What can be affected if Ethernet chooses the 2x12MPO interface is that the QSFP-DD MSA will need to further clarify

that there are two cases for the 2x12MPO – one for a module housing two transceivers, and another for a module housing a single transceiver. The former is what is handled now. The latter is missing. If the latter is added, and is permitted to be used for

applications that are not lane-number agnostic, then the current lane assignment numberings will need to be defined with a second alternative that is compatible with structured cabling.

Paul

From:

Brian Welch [mailto:bwelch@xxxxxxxxxxx]

Sent: Tuesday, April 24, 2018 2:47 PM

To: Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>;

Chris Cole <chris.cole@xxxxxxxxxxx>;

Jeffery Maki <jmaki@xxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>;

zshen@xxxxxxxxxx

Subject: RE: MPO-24 pin-out definition

I see a difference between single density and double density modules. For the case being discussed imagine

a 2x100G-PSM4 module, or in the future perhaps a 2x400G-DR4 module, the market views these differently than they would a 1x200G module or a 1x800G module insofar as they are essentially always used for breakout (ie, interface to two MPO12 based MDIs).

Not sure if it’s different for MMF solutions.

Brian

From:

Kolesar, Paul [mailto:PKOLESAR@xxxxxxxxxxxxx]

Sent: Tuesday, April 24, 2018 11:32 AM

To: Chris Cole <chris.cole@xxxxxxxxxxx>;

Jeffery Maki <jmaki@xxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>;

zshen@xxxxxxxxxx

Subject: RE: MPO-24 pin-out definition

Chris,

I don’t see anyone on this thread proposing to discard MPO16. But there was recognition that not everyone prefers

that interface. I know this from talking to people. And that’s why I anticipate debate.

You are right that in the past we have defined multiple MDIs. Just look at 100G-SR10 for a place where three configurations

were put into the standard.

I think the main question is whether the proposed MPO16 interface, said to be supported by many companies, should

be the only one in the standard. If the 2x12MPO interface is proposed by someone, what advantage does it offer, and is that advantage worth putting only it or both in the standard. To that end, a contribution citing some pros and cons for each alternative

would be helpful.

Paul

From:

Chris Cole [mailto:chris.cole@xxxxxxxxxxx]

Sent: Tuesday, April 24, 2018 1:50 PM

To: Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>;

Jeffery Maki <jmaki@xxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>;

zshen@xxxxxxxxxx

Subject: RE: MPO-24 pin-out definition

MPO16 is a known application, supported by many companies, so we should not be casually proposing to discard it. This

is not a way to build consensus.

http://www.ieee802.org/3/NGMMF/public/Mar18/shen_NGMMF_01a_mar18.pdf#page=2

If there is another application that requires MPO2x12, then the proponents need to put together a presentation showing

the applications and lining up supporters. Right now I don’t see a real application for SR8 in MPO2x12. It’s just a theoretical possibility.

If we determine, based on supported contributions, that there is also broad market potential for MPO2x12 SR8, we will

specify two connectors in the standard; MPO16 and MPO2x12. We have done that in the past when we had multiple connector requirements for the same PMD.

Chris

From:

Kolesar, Paul [mailto:PKOLESAR@xxxxxxxxxxxxx]

Sent: Monday, April 23, 2018 6:01 AM

To: Jeffery Maki <jmaki@xxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: [EXTERNAL]: RE: MPO-24 pin-out definition

Jeff,

I agree. The initial proposal for SR8 used the MPO16. There are others who prefer the 2x12MPO. I don’t know how

it will shake out.

Paul

From:

Jeffery Maki [mailto:jmaki@xxxxxxxxxxx]

Sent: Monday, April 23, 2018 8:55 AM

To: Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Paul,

Yes, so this shall likely have equal impact on QSFP-DD, OSFP, and COBO. A common module is likely going

to be looked to function as 400GBASE-SR8, 2 x 200GBASE-SR4, 4 x 100GBASE-2, 8 x 50GBASE-SR.

Jeff

From:

Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>

Sent: Monday, April 23, 2018 5:40 AM

To: Jeffery Maki <jmaki@xxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Jeff,

We are developing 400G-SR8 in 802.3cm. I believe there is going to be debate on the MDI lane assignments.

Paul

From:

Jeffery Maki [mailto:jmaki@xxxxxxxxxxx]

Sent: Monday, April 23, 2018 4:36 AM

To: Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>;

Brian Park <bpark@xxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Paul,

QSFP-DD, COBO and OSFP are striving to be the same in terms of electrical pin to optical port mappings.

Certainly, they are all striving to use a common management interface specification, The CMIS. If it were found to be of high merit for something new to be defined for OSFP, we should probably find that merit to extend to QSFP-DD and COBO too.

Is there something new emerging?

Jeff

From:

Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>

Sent: Sunday, April 22, 2018 7:13 AM

To: Brian Park <bpark@xxxxxxxxxx>;

Jeffery Maki <jmaki@xxxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

The below message was sent before complete. I have now completed it below.

Paul

From:

Kolesar, Paul

Sent: Sunday, April 22, 2018 9:44 AM

To: Brian Park <bpark@xxxxxxxxxx>;

Jeffery Maki <jmaki@xxxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: RE: MPO-24 pin-out definition

Brian,

I find it curiously restrictive of a transceiver with eight electrical inputs and eight electrical outputs to not

have the option to use an optical interface that offers the capacity for each of those signals to be carried on its own fiber. The MPO16 and 2x12MPO are the obvious choices to fill that vacancy.

With these interfaces there is no advantage that I can see for straying from the lane assignments of the QSFP-DD for

the MPO16. However, there should be debate on the lane assignments for the 2x12MPO.

As I understand the situation with the QSFP-DD, the lane assignments were selected to allow two optical engines, each

with four Tx and four Rx, to be placed such that each one occupies a row of the MPO. In effect this allows implementation by stacking two planar transceivers circuits, and was driven by how companies build 4-lane devices.

The question is whether that same mindset should be applied here.

There is an alternative for modules with more than four Tx and Rx, which is exemplified by the lane assignments defined

for 100G-SR10 and 400G-SR16. For these there is a row dedicated to Tx and a row dedicated to Rx.

The trouble with the QSFP-DD 2x12MPO assignments is that the two rows must each be broken out to be properly routed

over standardized structured cabling. This allows Tx1 to connect to Rx1. If not broken out, that Tx1 will connect to Rx5 because standardized structured cabling applies a lateral signal transposition and row transposition. This may be acceptable to protocols

that are lane agnostic, such as Ethernet, but that cannot be said for all applications.

To be complete, the same transpositions occur for any lane assignment (e.g. upper left connects to lower right), so

an existing alternative for a row of Tx over a row of Rx would need to consider that in its lane numbering for applications that are not lane-number agnostic. That means, for example:

Tx1 Tx2 … Tx7 Tx8

Rx8 Rx7 … Rx2 Rx1

Regards,

Paul

From:

Brian Park [mailto:bpark@xxxxxxxxxx]

Sent: Saturday, April 21, 2018 2:02 PM

To: Jeffery Maki <jmaki@xxxxxxxxxxx>

Cc: Chris Cole <chris.cole@xxxxxxxxxxx>;

Kolesar, Paul <PKOLESAR@xxxxxxxxxxxxx>;

Brian Welch <bwelch@xxxxxxxxxxx>;

Gary Nicholl (gnicholl) <gnicholl@xxxxxxxxx>;

Mark Nowell (mnowell) <mnowell@xxxxxxxxx>;

Tiger Ninomiya (Takuya) <Takuya.Ninomiya@xxxxxxxxx>;

John F Petrilla <john.petrilla@xxxxxxxxxxxxxxxx>;

Tom Palkert <tom.palkert@xxxxxxxxx>;

Sommers, Scott <Scott.Sommers@xxxxxxxxx>;

Brian Kirk <brian.kirk@xxxxxxxxxxxxxxxx>;

tommitcheltree@xxxxxxxxxxx;

Steve Hanssen <shanssen@xxxxxxxxxx>;

David Lai <davlai@xxxxxxxxxx>;

Hong Wang <hwang@xxxxxxxxxx>

Subject: Re: MPO-24 pin-out definition

Hi All,

I am afraid that I need to revive this year-old email thread- on the OSFP MSA and MPO lane assignment.

Last time we had discussion on the MPO16 and MPO24 (MPO12 two row) lane assignment; and in the OSFP MSA, those has

been not specified.

Senko (Tiger N.) commented to have MPO16 and MPO24 specification in OSFP MSA, same as QSFP-DD specification.

Below is latest QSFP-DD specification:

in OSFP-MSA, there is no MPO16 or MPO24. Frankly saying I wished stay away from the issue until industry settles before next revision.

A year passed, and I would like hear the opinion on this matter.

Thanks, Brian

To unsubscribe from the STDS-802-3-NGMMF list, click the following link: https://listserv.ieee.org/cgi-bin/wa?SUBED1=STDS-802-3-NGMMF&A=1