# DRAFT: 100 Gb/s per Lane for Electrical Interfaces and PHYs Call For Interest Consensus Presentation

CFI Target: IEEE 802.3 November 2017 Plenary

# Objective

- To gauge the interest and build consensus of starting a study group investigating a "100 Gb/s per lane for electrical interfaces and PHYs" project

- We do **not** need to:

- Fully explore the problem

- Debate strengths and weaknesses of solutions

- Choose a solution

- Create a PAR or 5 Criteria

- Create a standard

- Anyone in the room may vote or speak

### Higher speed copper transmission

What are the limits of copper?

- Higher speed copper was predicted to be dead a decade ago

but this has also been the case for the last 30 years

- Copper keeps on pushing the frequency limits

- Copper vs optical gap is closing as speeds increase

- Although optics offer reach and density, electrical still offers lower cost and power

- Equalization technology and modulation techniques continue to be improved

- PAM4, ENRZ, Duobinary, etc.

DATA COMMUNICATIONS

3

The economics at stake are huge, "Do you really want to bet against copper?"

# Motivation for 100 Gbps per Lane

- Parallel interfaces limit abilities

- Cost optimization (motivation for much of the industry)

- Maximize system efficiency

- 100Gbps per lane could be leveraged for many parts in the Ethernet family

Web-scale data centers and cloud based services are presented as leading applications

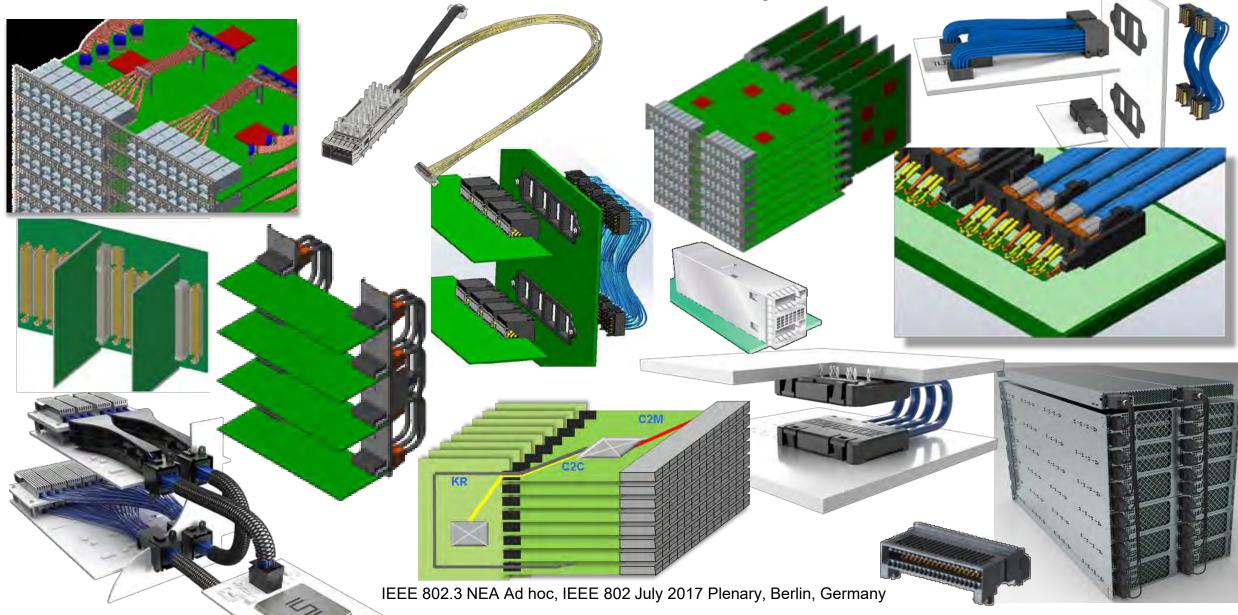

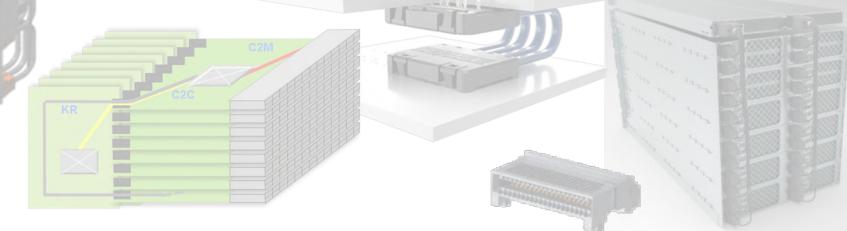

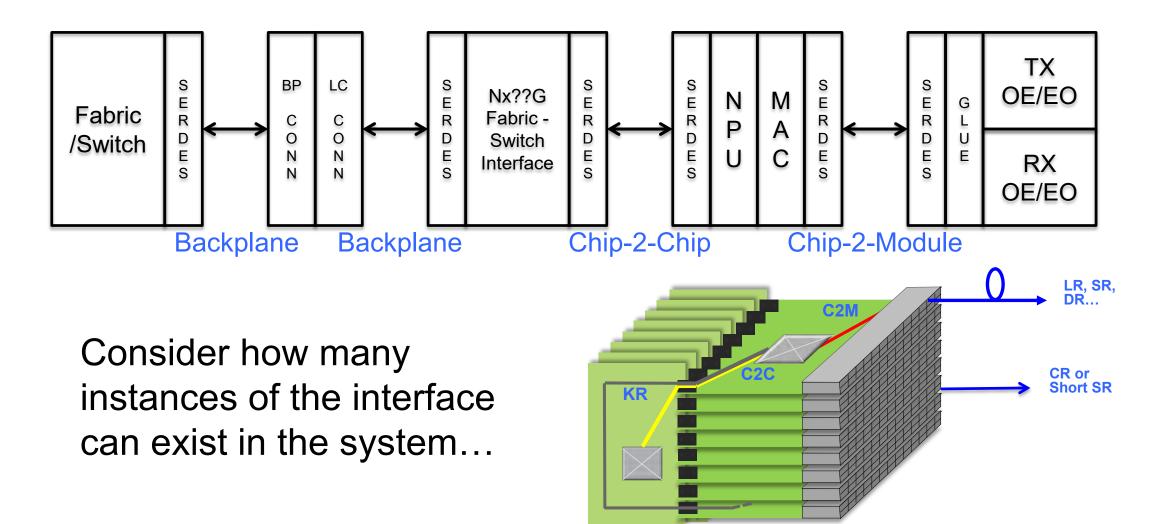

### Electrical interfaces come in many shapes and sizes.

# **Tonight's Meeting**

• To present the

### market **NEED**, technical **Feasibility**,

and *impact* on relevant PHYs and data rates

of 100Gbps/lane-based electrical signaling.

- To gain consensus towards Call-for-Interest to form a study group.

- We are NOT discussing specific implementations or objectives these are just some of the reasons that we <u>need</u> a study group!

### Market Drivers 100 Gb/s per Electrical Lane Ethernet Market Drivers -

## High Speed Front End Interconnects The Road Map of Port Rates

# The Ethernet Family (100 Gb/s and Above)

|           | Signaling<br>(Gb/s) | Electrical<br>Interface | Backplane | Twin-<br>ax | MMF  | 500m<br>SMF | 2km<br>SMF   | 10km<br>SMF | 40km<br>SMF |

|-----------|---------------------|-------------------------|-----------|-------------|------|-------------|--------------|-------------|-------------|

| 100GBASE- | 10                  | CAUI-10                 |           | CR10        | SR10 |             | <u>10X10</u> |             |             |

|           | 25                  | CAUI-4 /<br>100GAUI-4   | KR4       | CR4         | SR4  | PSM4        | CWDM4 CLR4   | LR4         | ER4         |

|           | 50                  | 100GAUI-2               | KR2       | CR2         | SR2  |             | -            |             |             |

|           | 100                 | ?                       | ?         | ?           |      | DR          |              |             |             |

| 200GBASE- | 25                  | 200GAUI-8               |           |             |      |             |              |             |             |

|           | 50                  | 200GAUI-4               | KR4       | CR4         | SR4  | DR4         | FR4          | LR4         |             |

|           | 100                 | ?                       | ?         | ?           |      |             |              |             |             |

| 400GBASE- | 25                  | 400GAUI-16              |           |             | SR16 |             |              |             |             |

|           | 50                  | 400GAUI-8               |           |             |      |             | FR8          | LR8         |             |

|           | 100                 | ?                       | ?         | ?           |      | DR4         |              |             |             |

Includes Ethernet standards in development

<u>Underlined</u> – indicates industry MSA or proprietary solutions

# What Are We Talking About?

## Interface Width: High Level Math

- System Connections

- Consider a system has 10s of thousands of interconnects (say 15k)

- For the same throughput:

- 25Gbps/lane "by 4" → 60k interfaces

- 100Gbps/lane "by 1" → 15k interfaces

- Pin Count of a 10Tb chip

| Speed/lane | # Lanes in 1Tbps | # Balls Needer |           |

|------------|------------------|----------------|-----------|

| 10 Gbps    | 1000             | 4000 🔸         |           |

| 25 Gbps    | 400              | 1600 🚽         | > Yikes!! |

| 100 Gbps   | 100              | 400 🖌          |           |

Enabling higher

throughput

\* Single lane = 2 differential pairs (4 balls)

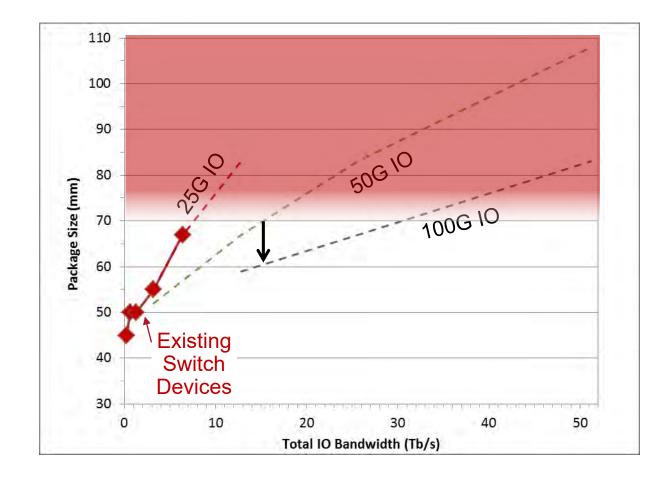

### IO Escape forcing transition to higher lane speeds

- ~ 70mm package is a current BGA practical maximum (due to coplanarity / warpage)

- This will force BGA devices with > 14Tb/s of aggregate bandwidth to transition to lane rates of higher greater than 50G (possibly 100G?) IEEE 802.3 NEA Ad hoc, IEEE 802 July 2017 Plenary, Berlin, Germany

## IO Escape forcing transition to higher lane speeds

This will force BGA devices with > 14Tb/s of aggregate bandwidth to transition to lane rates of higher greater than 50G (possibly 100G?)

## **Technical Feasibility**

100 Gb/s per Electrical Lane Ethernet Technical Feasibility -

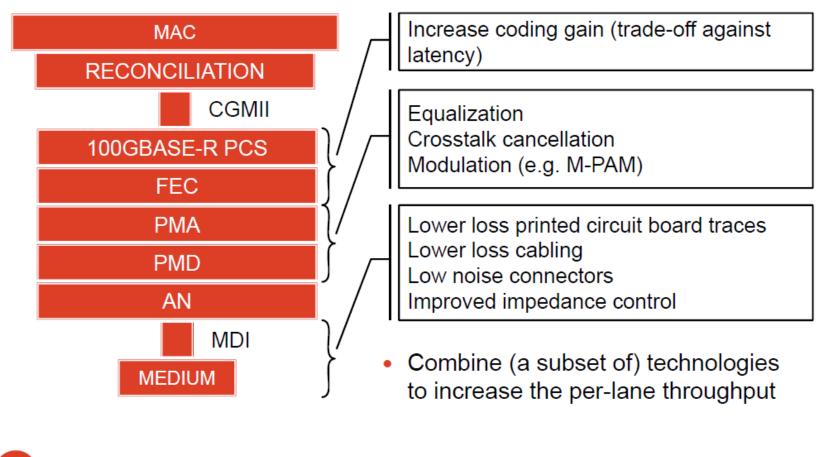

## The Story Hasn't Changed

- From 25G Backplane CFI

<u>http://www.ieee802.org/3/cfi/1</u>

<u>110\_1/CFI\_01\_1110.pdf</u>

- "Knobs" for tuning are the same; some have extended their scope, but it's still the same list.

- Now is the time to rebalance for the next speed!

### Potential enablers for more Gb/s/lane

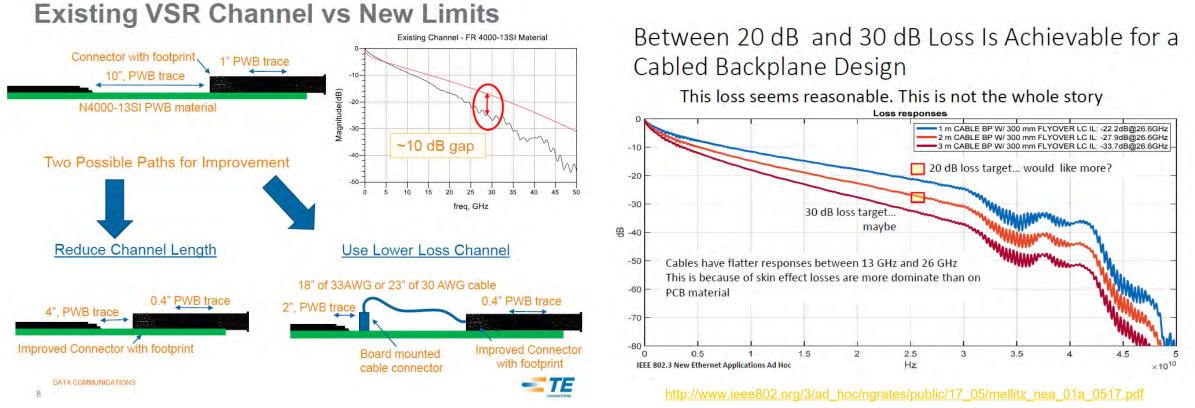

# Not-your-Grandmother's Channel

• 25G NRZ channels may be too high loss,

### but we have options to study.

http://www.ieee802.org/3/ad hoc/ngrates/public/17 05/tracy nea 01 0517.pdf

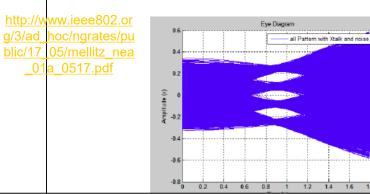

### PHY Simulation Shows Promising Results

□ BER is about 6.2E-8.

TX FIR: 3 pre cursors, 25 post cursors, tail taps are very small. □ RX: CTLE + DFE.

> DSP

using PAM-4

Of course follow-on work will happen.

MACOM

3

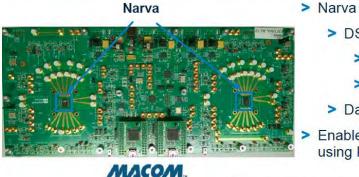

#### Narva: **Proof of Concept Vehicle for 100Gbps SERDES**

#### > DAC output @53.125GBaud

Tx and Rx Equalization

> Data Converters ADC and DAC.

> PRBS31 generator and checker.

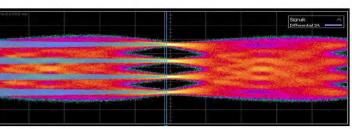

# **Proof of Concepts** Shown

#### **100G Short Reach Design Results**

- A 100Gb/s PAM4 SERDES for short reach has been developed and demoed.

- With 28nm process node, TX eye is clean. Multiple tap TX FIR has been applied for TX eye measurement.

Test Setup

http://www.ieee802.or

/3/ad\_hoc/ngrates/pi blic/17 05/sun nea 0

1a 0517.pdf

#### 02 0517.pdf July 2017 Plenary, Berlin, Germany

### PHY Simulation Shows Promising Results

BER is about 6.2E-8.

TX FIR: 3 pre cursors, 25 post cursors, tail taps are very small.

RX: CTLE + DFE.

# Further Study Needed – Optimize and Tune

## Why Now??? 100 Gb/s per Electrical Lane Ethernet Timing -

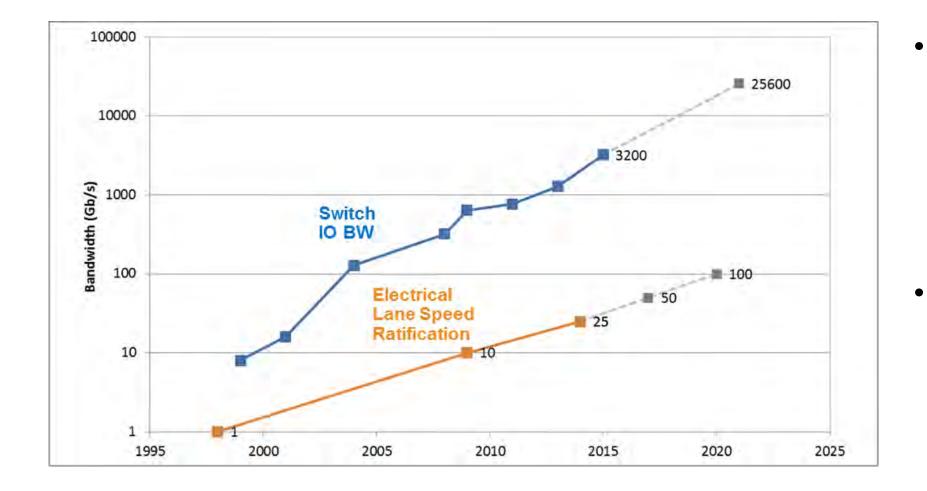

## Historical Perspective – Why 100G Now?

- Historical curve fit to highest rate switch products introduced to market (blue squares)

- Single ASIC IO capacity doubling every ~ 2 years

## **Enable the Future**

|           | Signaling<br>(Gb/s) | MMF  | 500m<br>SMF | 2km<br>SMF   | 10km<br>SMF | 40km<br>SMF |

|-----------|---------------------|------|-------------|--------------|-------------|-------------|

| 100GBASE- | 10                  | SR10 |             | <u>10X10</u> |             |             |

|           | 25                  | SR4  | PSM4        | CWDM4 CLR4   | LR4         | ER4         |

|           | 50                  | SR2  |             | _            |             |             |

|           | 100                 |      | DR          |              |             |             |

|           | 25                  |      |             |              |             |             |

| 200GBASE- | 50                  | SR4  | DR4         | FR4          | LR4         |             |

|           | 100                 |      |             |              |             |             |

| 400GBASE- | 25                  | SR16 |             |              |             |             |

|           | 50                  |      |             | FR8          | LR8         |             |

|           | 100                 |      | DR4         |              |             |             |

Not a statement of objectives, however this effort has the potential to impact many areas of the industry.

$\bullet$

Includes Ethernet standards in development

<u>Underlined</u> – indicates industry MSA or proprietary solutions

## The Interest is Here

Straw Poll #2

- Is there interest in developing AUI's based on 100 Gb/s electrical signaling per lane?

- Results

- Yes 43

- No 2

- Maybe 15

Straw Poll #3

- Is there interest in developing Backplane / Copper Cable PHYs based on 100 Gb/s electrical signaling per lane?

- Yes 18

- No 10

- Maybe 20

March 2017\*\*

## Straw Polls

May 2017\* 🔶

Taken from NEA Ad Hoc unapproved Minutes

- \* http://www.ieee802.org/3/ad hoc/ngrates/public/17 05/minutes nea 0517 unapproved.pdf

- \*\* http://www.ieee802.org/3/ad hoc/ngrates/public/17 03/minutes nea 0317 unapproved.pdf

IEEE 802.3 NEA Ad hoc, IEEE 802 July 20<sup>-</sup>

Straw Poll #1

- I would support development of a CFI that includes:

- a) new backplane PHY,

- b) new Passive Copper Cable PHY

- c) Chip-to-chip (C2C AUI)

- Chip-to-module (C2M AUI)

- other e)

32

26

40

48

0

2

- not at this time.

- g) none of the above

Results

a)

b)

C)

d)

e)

f)

g) 0 Areas of Study

- 1. Chip-to-Chip AUI

- 2. Chip-to-Module AUI

- 3. Backplane

- 4. Potential changes of existing PHYs

NOTE: This is not a laundry list of items to be debated today, but this CFI enables study in these areas.

# Summary

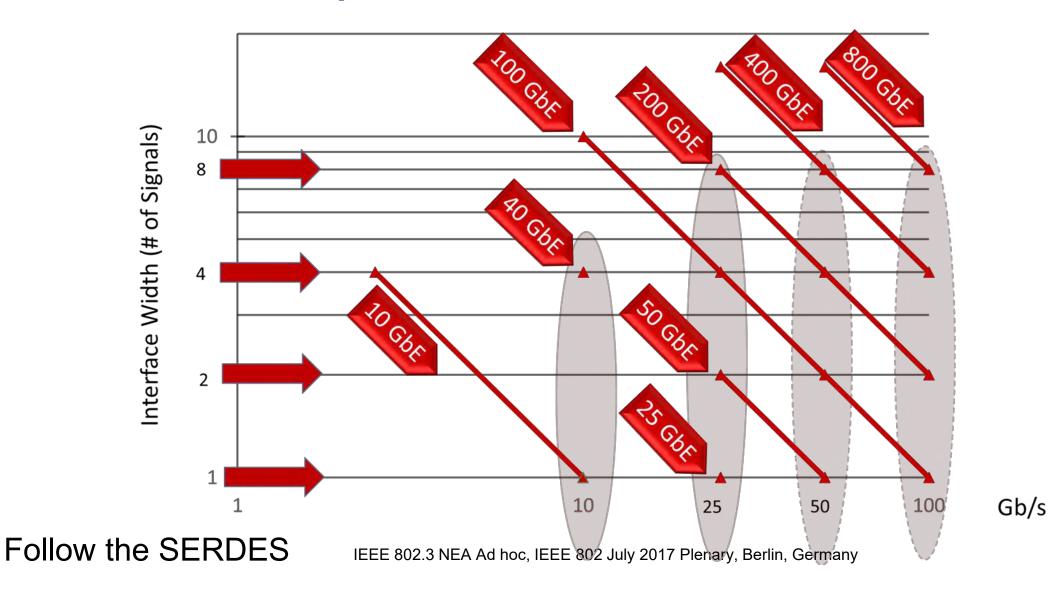

- 100 Gb/s is the next step on "Follow the SerDes" and continues existing market trends

- Switching capacity progression

- Reduction of interface width

- 100 Gb/s per lane seems feasible with a few tools still available

- Impact of 100 Gb/s Electrical Signaling is broad across the Ethernet Family

- AUIs for existing PHYs for existing rates

- For new PHYs for existing rates

- New AUI's / PHYs for new rates?

- Let's form a Study Group!!

# **Straw Polls for CFI**

# Call-for-Interest Consensus

- Should a study group be formed for "100 Gigabit/s per Lane for Electrical Interfaces and PHYs"?

- Y: N: A:

• Room count:

# Participation

- I would participate in a "100 Gigabit/s per Lane for electrical interfaces and PHYs" study group in IEEE 802.3

- Tally:

- My company would support participation in a "100 Gigabit/s per Lane of Electrical Interfaces and PHYs" study group

- Tally:

# Future Work

- Ask 802.3 at Thursday's closing meeting to form a "100 Gigabit/s per lane for electrical interfaces and PHYs" study group

- Prepare ITU liaison letter for WG approval if Study Group formation is approved by WG.

- If approved:

- 802 EC informed on Friday of formation of the study group

- First study group meeting would be during January 2018 IEEE 802.3 interim meeting