## FEC Proposal for NGEPON – update (rev 1a)

#### Mark Laubach, Shaohua Yang, Yang Han, Ryan Hirth, Glen Kramer

6 November 2017 IEEE 802/802.3 Plenary, Orlando Florida

P802.3ca November 2017 plenary meeting

#### Introduction

- An LDPC(18493,15677) [11x74x256] 0.848 rate FEC code, code matrix, and interleaver was

proposed at the May 2017 meeting

- laubach 3ca 1 0517 with update laubach 3ca 4 0517

- This presentation introduces an updated "New" LDPC(18493,15677) [13x75x256] 0.848

- Increased use of parity word puncturing for improved correction performance

- Motivation from jinyinrong\_3ca\_2b\_0717

- Error floor below BER 1x10<sup>-12</sup> (meets TF Objective)

- Iterations capped at 15

- Author's LDPC proposal is updated

- Recommend code matrix and puncturing from this presentation

- AWGN and Gilbert burst error models are studied

- Pre-coding and Gilbert burst study is still in progress as of 10/27/17.

- Impact of Omega256 structured and random interleaving is reviewed.

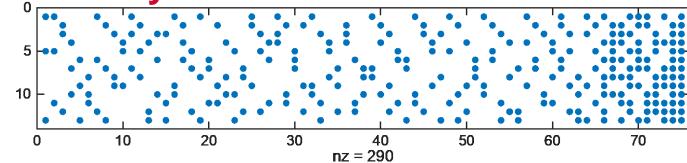

#### **Proposed New Parity Check Matrix**

#### Puncturing:

- 512 bits punctured

- Location from right side of the H matrix (two circulants with weight 12 and 13)

Parity Word Shortening:

- 195 bits shortened

- Location from the left side of the H matrix (the circulant with weight 3)

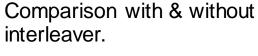

#### Use shortening to support handling of different burst lengths

- Upstream, set to zero for the bits corresponding to shortened locations during encoding. Encode normally for the full length of the code. Shortened bits are not transmitted.

- Downstream, set to maximum LLR at decoder input for shortening locations. Decode normally for the full length of the code.

- Decoding complexity/latency stays the same

- Shortening doesn't degrade error floor performance. If the shortening locations are carefully chosen, shortening will improve error floor performance

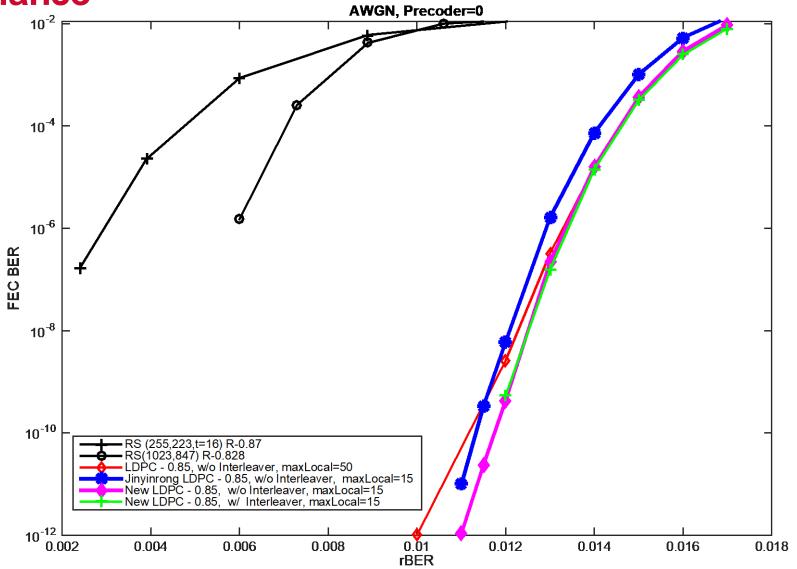

#### **AWGN Performance**

Note: interleaver provides no additional performance gain for AWGN only model as expected.

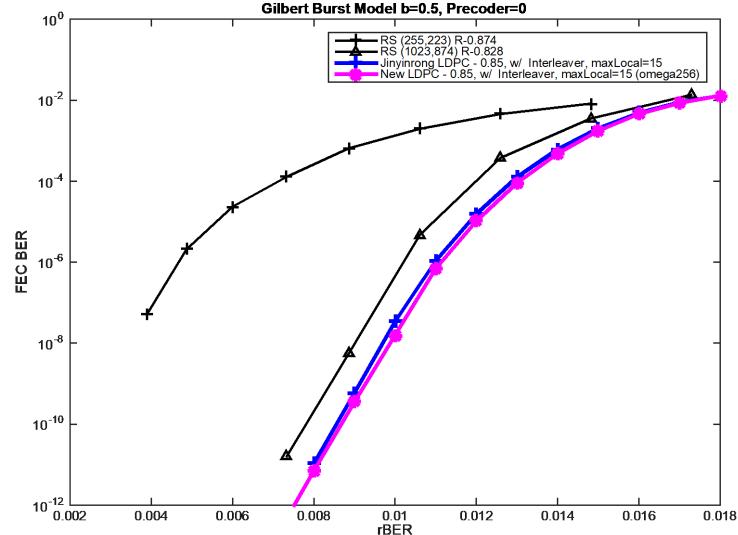

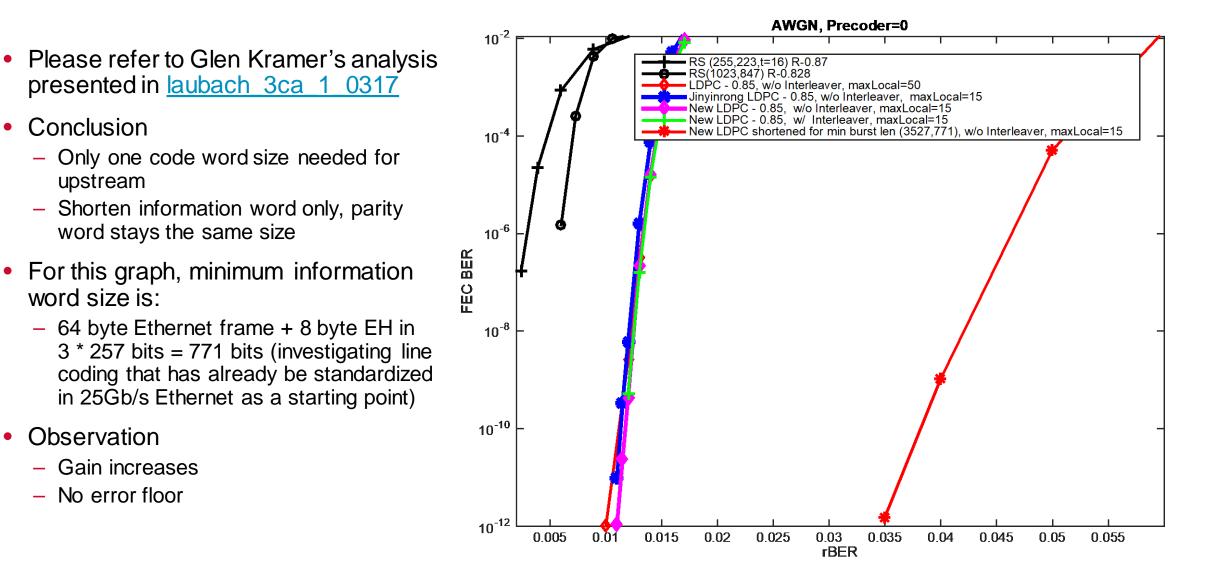

#### **Gilbert burst error performance**

Note 1: with "hardware friendly" local Omega256 interleaver presented in laubach\_3ca\_1\_0517.

Note 2: original Omega256 interleaver was optimized for use with precoding. No precoding is used in this presentations studies.

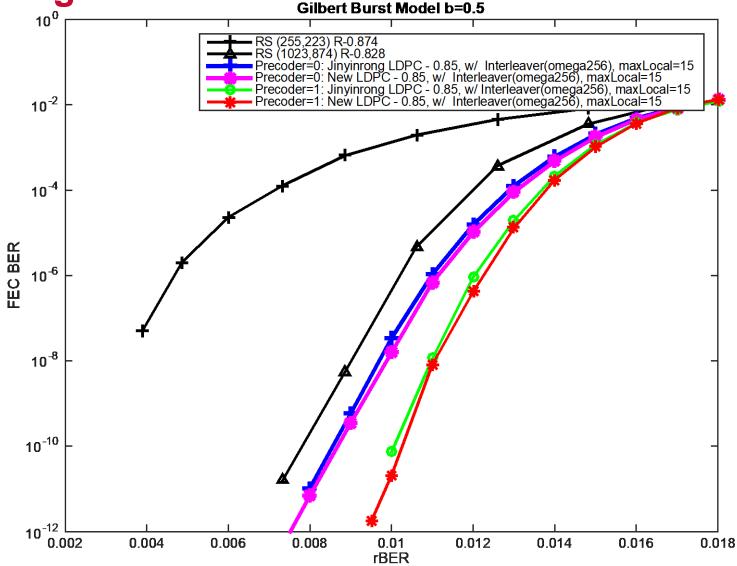

#### Gilbert burst error performance "zoom in"

Gilbert Burst Model b=0.5, Precoder=0 10<sup>--</sup> Jinyinrong LDPC - 0.85, w/o Interleaver, maxLocal=15 Jinyinrong LDPC - 0.85, w/ Interleaver, maxLocal=15 New LDPC - 0.85, w/o Interleaver, maxLocal=15 New LDPC - 0.85, w/ Interleaver, maxLocal=15 (omega256)  $10^{-5}$ New LDPC - 0.85, w/ Interleaver, maxLocal=15 (rnd Itivr)  $10^{-6}$ 10-7 FEC BER 10<sup>-8</sup> 10<sup>-9</sup>  $10^{-10}$ 10<sup>-11</sup> 10<sup>-12</sup> 7.5 8.5 9 9.5 10 10.5 11 11.5 12 **∦ 10<sup>-3</sup>** rBER

"Omega256" is a local interleaver sized for spanning a single circulant of 256 bits.

"Random" intereaver spans the entire codeword.

Observation: random interleaver provides better performance but at increased complexity.

#### FEC Code Gains, sizes, and latencies

|      | Length                                    | Rate  | Non-<br>Zero<br>Blocks | NECG <sup>1</sup> (dB)<br>(optical gain) |                                                                  | M Gates                              | Latency <sup>3</sup>                |                        |

|------|-------------------------------------------|-------|------------------------|------------------------------------------|------------------------------------------------------------------|--------------------------------------|-------------------------------------|------------------------|

|      |                                           |       |                        | AWGN                                     | Gilbert<br>Burst <sup>2</sup>                                    | Encoder + Decoder<br>(approximately) | (µsec)<br>(includes single buffer)  | Reference              |

| LDPC | (18493,15677)<br>[11x74x256] <sup>7</sup> | 0.848 | 382                    | 2.46<br>(1.7-2.2)                        | 1.85<br>(1.3-1.8)                                                | 1.65 to 1.8                          | E 2.77 + D 2.95 = 5.72 <sup>4</sup> | laubach_3ca_1_0517     |

|      | (18493,15677)<br>[13x75x256]              |       | 290                    | 2.6<br>(1.8-2.3)                         | 1.76 <sup>5</sup><br>(1.2-1.6)<br>1.87 <sup>6</sup><br>(1.2-1.7) |                                      |                                     | This presentation.     |

|      | (18493,15677)<br>[13x76x256] <sup>8</sup> |       | 296                    | 2.56<br>(1.8-2.3)                        | 1.75<br>(1.2-1.8)                                                | 3.4                                  | -na-                                | jinyinrong_3ca_2b_0717 |

| RS   | (1023, 847)                               | 0.828 | -na-                   | <b>1.34</b> (0.94-1.2)                   | <b>1.35</b><br>(0.95-1.2)                                        | 1.06                                 | E+D:0.77                            |                        |

<sup>1</sup> Electrical gain over RS(255,223) of 7.1 dB. Optical gain is 0.7 to 0.9 \* NECG

<sup>2</sup> Gilbert Burst (with interleaver, no precoding)

<sup>3</sup> Capped at 15 iterations

<sup>4</sup> Implementation dependent: LDPC encoding and decoding latency can be reduced with more parallel operations, with the cost of additional area; e.g. encoder could be reduced from 2.0 to 0.94 by adding more complex multipliers. In decoder latency could be reduced by lowering the iteration cap, however this needs further study.

<sup>5</sup> Hardware friendly interleaver <sup>7</sup> [11x74ex256] code gain first presented is based on 50 max iteration

<sup>6</sup> Full random interleaver

<sup>8</sup> From our own simulation Jinyinrong code gain is 2.56 dB on AWGN and 1.75 dB on Gilbert with max 15 local, hardware friendly interleaver

#### **On Shortening methodology**

#### **New Slide**

•

•

#### **On processing latency**

#### **New Slide**

- Several good awareness raising presentations on eCPRI and 3GPP

- Lowest one-way latency comes from eCPRI at 100 µsec (3GPP 250 µsec)

- Was hoping to see proposals on one-way latency budgets for P802.3ca

- Like optical power budget, need to understand what latency gets allocated between the test points for the measurement, separate for downstream and upstream e.g.:

- Propagation delay (what is our maximum support distance?)

- OLT processing (includes FEC)

- ONU processing (includes FEC and any upstream scheduling latency considerations)

- Until then a total one-way FEC latency contribution < 10% (10 µsec) seems reasonable

#### **New Slide**

#### Impact of using pre-coding "on the wire"

We had a request to look at performance for Gilbert burst + precoding

### Summary

- Updated "New" LDPC(18493,15677) [13x75x256] 0.848 rate, using puncturing and min-sum decoding sufficiently provides a NECG that meets error performance using 10<sup>-2</sup> raw input, with an error floor below the Task Force BER objective of 1x10<sup>-12</sup>.

- The authors continue to recommend selection of LDPC as the FEC method for P802.3ca

- Recommend code matrix and puncturing from this presentation

- Original Omega256 interleaving technique provides small gain with Gilbert burst error model for both the Jinyinrong and "New" LDPC codes studied.

- Was optimized for a noise environment that included pre-coding in original studies

- Other local interleaver optimizations for AWGN only and Gilbert burst only noise models may or may not provide advance beyond random interleaver.

### Thank you

# **BROADCOM**<sup>®</sup> connecting everything ®