#### Timing in PHY startup (D2.1 Comment #169)

IEEE P802.3ch Multigig Automotive Ethernet PHY Task Force Ad Hoc

George Zimmerman ((General) Ad Hoc Chair), CME Consulting, Inc

#### Comment 169

C/ 149 SC 149.4.2.4.10

P **147**

L 35

# 169

Razavi, Alireza

Aquantia

Comment Type

Comment Status X

late

To ensure interoperability during the training phase, certain timing allocations between Master, Slave and other steps of training must be observed. We propose to the text of 802.3bz for interoperability and just scale the timing of 10G mode and deduct the timing for PCS\_TEST that is set by min\_wait\_timer.

#### SuggestedRemedy

tModify Figure 149\_33 as attached and Include the associated Table 145.15 in section 149.4.2.4.10 page 147, line 35 to read as follows

MASTER SLAVE MAX REQUIRED TIME

-----

| Traning         | Silent          | 40.00 msec |

|-----------------|-----------------|------------|

| Training        | Training        | 57.02 msec |

| <b>PCS Test</b> | <b>PCS Test</b> | 0.98 msec  |

| TOTAL           |                 | 98.00 msec |

Proposed Response

Response Status O

## Timing the startup

- PHY control must complete in no more than 97 msec or risk being terminated by the link\_fail\_inhibit\_timer

- 97 msec, Max = 98 msec (see 98.5.2)

- No timers control times in:

- SILENT

- TRAINING

- COUNTDOWN/TX\_SWITCH

- Experience from 10GBASE-T showed different designers made different assumptions of the time distribution

- Discovered after initial publication, so it was a recommendation, not a requirement

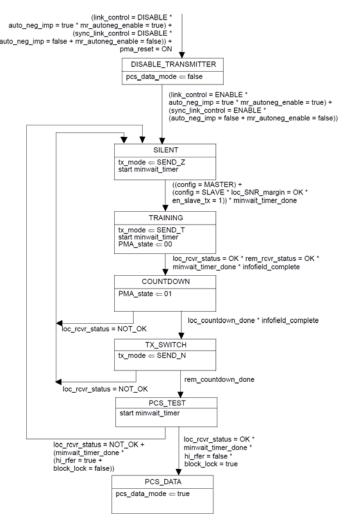

Figure 149–33—PHY Control state diagram

#### Approaches to the problem

- Modify state diagram: Add timers to push on to the next state

- This makes us define the behavior in the over-time case which isn't supposed to happen: EXTRA WORK & UNINTENDED CONSEQUENCES!

- Add a statement "a compliant phy shall spend no more than X msec in state Y" into state diagram text

- Such statements get lost and are unusual in 802.3 style

- Add a table for timing, similar to 2.5G/5G/10GBASE-T, but REQUIRED.

### Suggested response

Insert new final paragraph to 149.4.2.4.10 Startup sequence (Page 147 line 35): "The startup timing shall comply with Table 145-15."

Insert new table 145-15 at end of 149.4.2.4.10

Table 145-15: Maximum time spent in startup states (See Figure 149-33)

| MASTER                                           | Maximum time (msec) | SLAVE                      |

|--------------------------------------------------|---------------------|----------------------------|

| SILENT plus (TRAINING state AND en_slave_tx = 0) | 40                  | SILENT                     |

| TRAINING state AND en_slave_tx = 1)              | 54.439              | TRAINING                   |

| COUNTDOWN plus TX_SWITCH                         | 0.384 / S           | COUNTDOWN plus TX_SWITCH   |

| PCS TEST                                         | 1.025               | PCS TEST                   |

| Total (for reference only)                       | 95.464 + 0.384/S    | Total (for reference only) |

# THANK YOU!

#### Consensus WE BUILD IT.

Connect with us on:

Facebook: https://www.facebook.com/ieeesa

**Twitter:** @ieeesa

in LinkedIn: http://www.linkedin.com/groups/IEEESA-Official-IEEE-Standards-Association-1791118

IEEE-SA Standards Insight blog: http://standardsinsight.com

YouTube: IEEE-SA Channel

IEEE

standards.ieee.org

Phone: +1 732 981 0060 Fax: +1 732 562 1571

© IEEE