## **Key Assumptions**

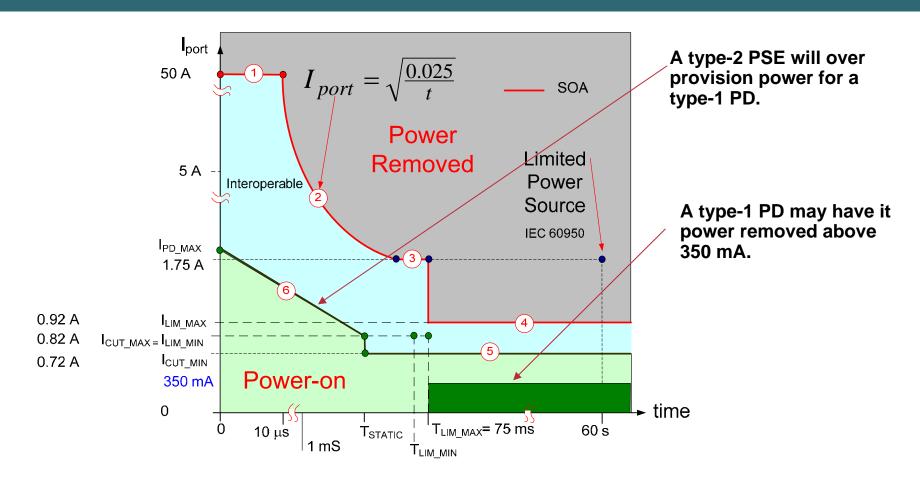

- PD current limiting only needs to be done by PDs that go outside the green interoperability zone.

- The IEEE specification complaince ensures interoperability.

- IEC 60950 compliance ensures safety.

- The design space should be opened up.

- Requirements should support real systems.

- One curve set should support legacy and PoE plus.

# **Agreement Areas**

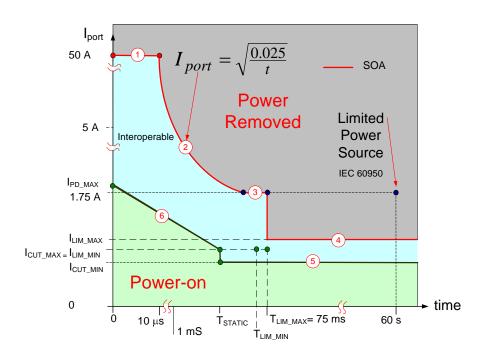

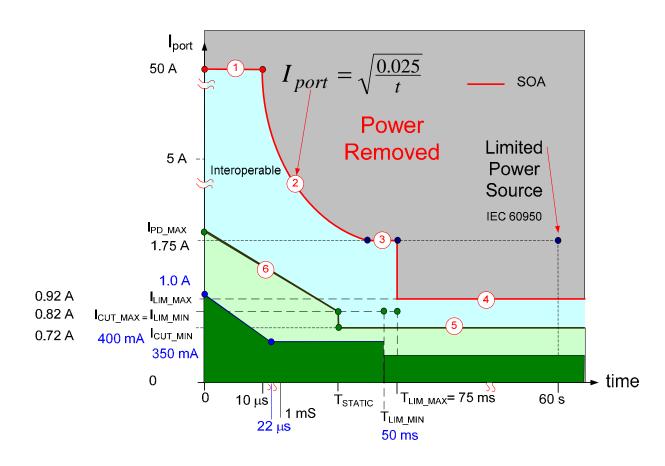

- PSE SOA

- Need for PD current threshold tolerance.

- Need for PD ripple current.

### Key Difference: How to support PD current ripple

- PoE plus need for I<sub>CUT\_MAX</sub> for T<sub>LIM\_MIN</sub>?

No PD tested for ad hoc work exceed I<sub>CUT</sub>.

- The shape of the system interoperability curve for t < 3 ms.</li>

A square region requires PD current limiting or PSE over design for a generic PD.

A triangular region allows most PDs to omit current limiting but does not prevent current limiting from being used.

## **Creating the PSE SOA**

#### (4) Average Current

- There are no controls on how often a PSE voltage may change due to PD load changes.

- The repetition of the worstcase event is unlikely. Therefore, removing power when a PD exceeds P<sub>CLASS</sub> for at least 1 s is acceptable.

- Preserve existing system tolerances,

I<sub>LIM\_MAX</sub>/I<sub>CUT\_MIN</sub> = 450/350

$$I_{\text{LIM\_MIN}}/I_{\text{CUT\_MIN}} = 400/350$$

The long term system cable average is I<sub>CUT MIN</sub>.

$$I_{LIM\_MAX} = 720 \times 450/350 = 920 \text{ mA}$$

$$I_{\text{CUT MIN}} = I_{\text{CABLE}} = 720 \text{ mA}$$

$$T_{LIM\ MIN} = f(I_{LIM})$$

## **Creating the PSE SOA**

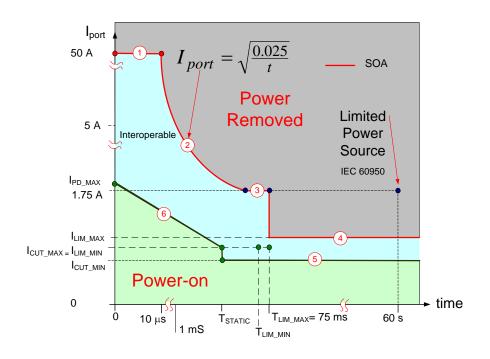

A current limiting PSE

Provides I<sub>LIM</sub> for T<sub>LIM</sub>

PD power is removed above  $T_{LIM}$  or when Pclass has been exceed for 1 s.

Provides enough power to ensure the system can operate within the green zone. PD power is removed above the energy base limit.

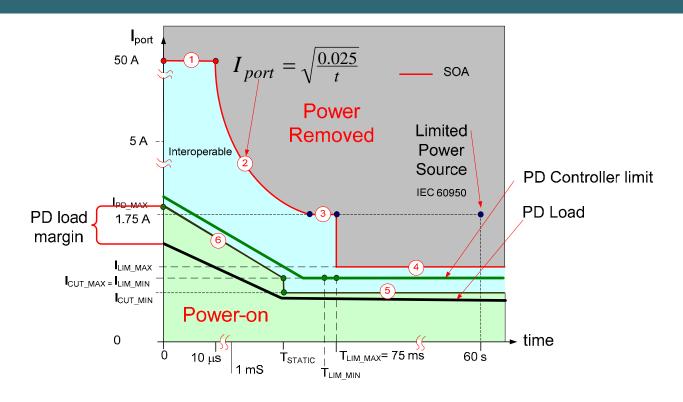

#### (5) Average Current

- The PD is designed to draw less than I<sub>CUT\_MIN</sub> with a static port voltage.

- PD power compliance may be checked over a period of 1s.

- A PD design must remain within the green zone and this provides "design room."

A PD with less capacitance than is permitted will be well below the green boundary. The excess margin can be used to support PD current noise.

The specification should provide a system model to use.

The PD design ensures the average current is within the green zone and may draw the maximum allowable power.

The PD silicon may limit the current above the green zone.

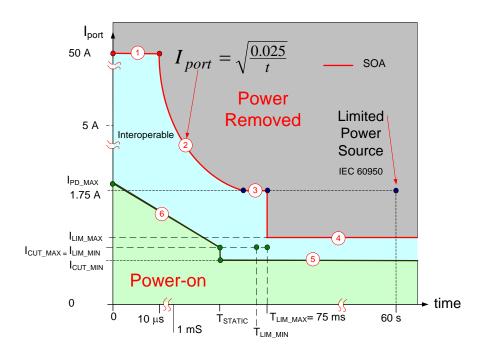

#### (6) Transient Current

- During permitted system voltage changes the PD shall limit its current to values within the green zone.

- A PD with less capacitance than is permitted will be below the green boundary. The excess margin can be used to support PD current ripple.

- The specification should provide a system model to use.

Real PD DC-DC operate near 100 kHz (T =  $10\mu$ s). What are our needs for real repetitive current ripple?

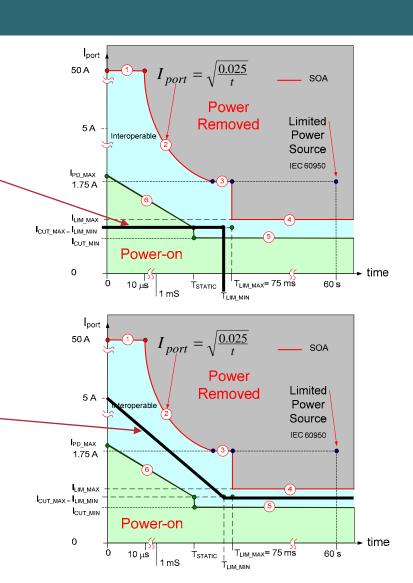

This shows a legacy PD reusing the terminology of the proposed AT curve.

This shows a legacy PD within the proposed AT curve.

This shows a proposed type-2 PSE AT/legacy curve.