CJ Clark, Intellitech Corp.

IEEE 1149.1 PDL tutorial - CJ Clark, Intellitech Corp. Business-wise some have chosen to focus on EXTEST or the boundary register - that is fine, it doesn't change the original scope of 1149.1

## 1. Overview

## 1.1 Scope

This standard defines test logic that can be included in an integrated circuit to provide standardized

approaches to

testing the interconnections between integrated circuits once they have been assembled onto a printed circuit board or other substrate;

- testing the integrated circuit itself; and

observing or modifying circuit activity during the component's normal operation.

The test logic consists of a boundary-scan register and other building blocks and is accessed through a Test Access Port (TAP). Some parts of 1149.1 have not addressed complexity of IC design well to accomplish a) and c) - i.e. Runbist

## 1.2.2 The use of IEEE Std 1149.1 to test an assembled product

This subclause outlines the use of the boundary-scan circuitry defined by this standard during the process of testing an assembled product such as a printed circuit board.

The test problem for any product constructed from a collection of components can be decomposed into three goals:

a) To confirm that each component performs its required function;

b) To confirm that the components are interconnected in the correct manner; and

c) To confirm that the components in the product interact correctly and that the product performs its intended function.

While respect is provided to those who want to use just the EXTEST part of the standard, the converse also must adhere for those who have used the standard as it was originally described.

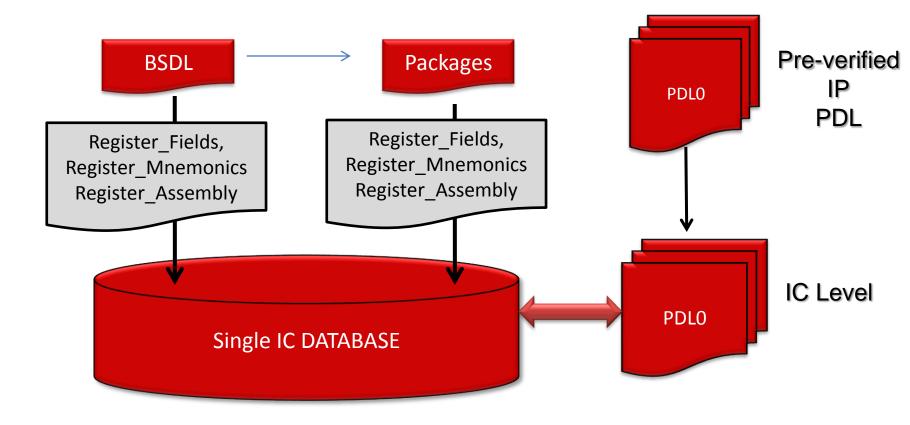

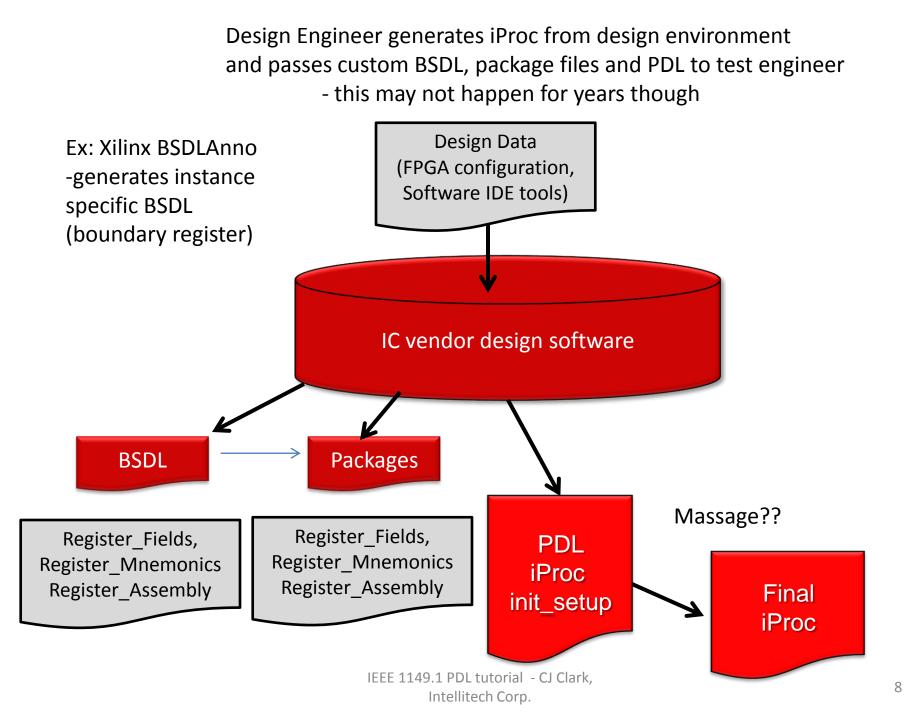

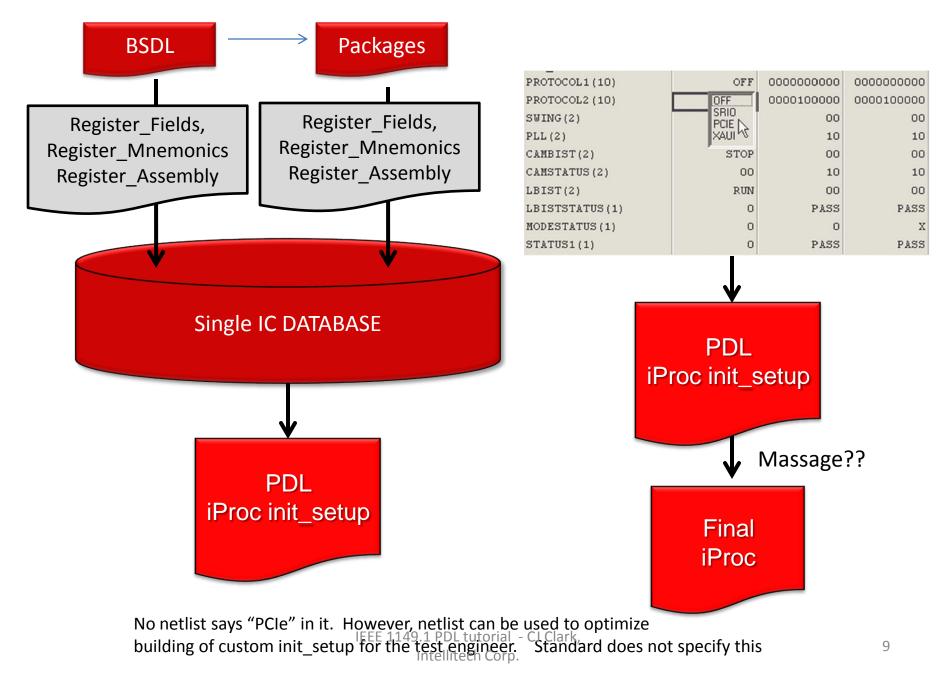

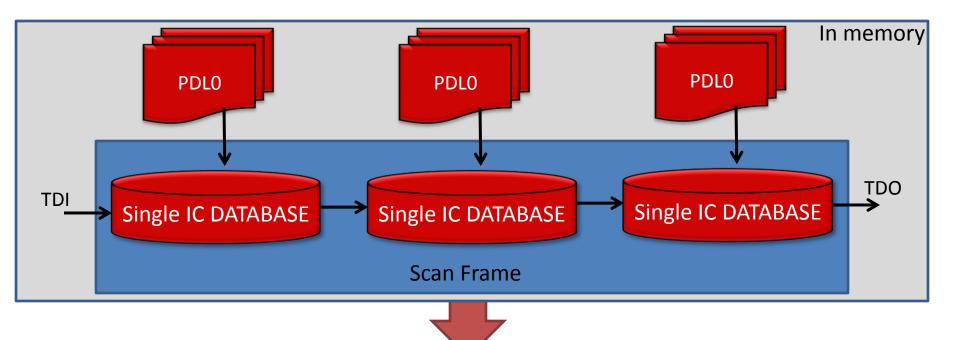

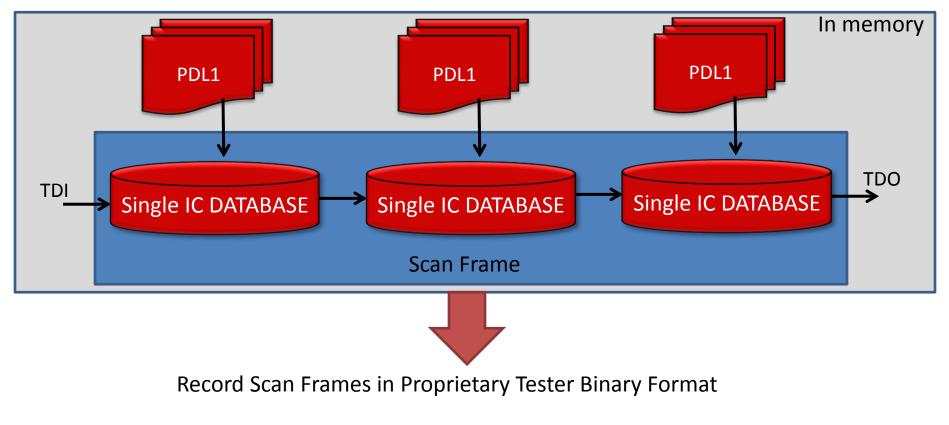

How PDL works:

Basic concept is that BSDL and package files are combined to make a single IC database which is operated on by PDL

- Tool vendors combine single IC databases into board scan chains

- Tool vendors have had proprietary macros/languages before BSDL this is not new or unproven territory

# A look at how PDL operates on scan database

| init-data<br>CAPTURES fills in<br>RESETVALs on cel | iWrite (in)<br>UU<br>iExpected<br>ls without PI fill in iE    | iRead (expected)<br>XX                           | TDO (OUT)<br>XX                            | During<br>Pattern<br>Generation<br>TDO is not   |

|----------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------|--------------------------------------------|-------------------------------------------------|

| Without any scan<br>init-data                      | s you may have expo<br>iWrite (in)<br>UU<br>Tool vendors choi | iRead (expected)<br>0x11                         | TDO (OUT)<br>XX<br>n when nothing in field | Looked at<br>As the UUT<br>Is not<br>Connected. |

| DEFAULT and SAF                                    | E values can initializ                                        | e iWrite field                                   |                                            |                                                 |

|                                                    | iWrite (in)                                                   | iRead (expected)                                 | TDO (OUT)                                  |                                                 |

| init-data                                          | 0x01                                                          | 0x11                                             | ХХ                                         |                                                 |

| after iWrite init-d                                | ata 0x55, database                                            | holds 0x55                                       |                                            |                                                 |

|                                                    | iWrite (in)                                                   | iRead (expected)                                 | TDO (OUT)                                  |                                                 |

| init-data                                          | 0x55                                                          | 0x11                                             | XX                                         |                                                 |

| •                                                  | •                                                             | ss'/warnings if new iW<br>ning, but tool provide | rite data overwrites a S.<br>r choice      | AFE value                                       |

| after iRead init-da                                | nta(1) 1, database h                                          |                                                  |                                            |                                                 |

|                                                    | iWrite (in)                                                   | iRead (expected)                                 | TDO (OUT)                                  |                                                 |

| init-data                                          | 0x55                                                          | EEOx139.1 PDL tutorial                           | c <b>Yč</b> lark,                          | 5                                               |

Intellitech Corp.

5

| Register_fields | are just pointers | to bits. iWrite m | ysinglebit 0 |

|-----------------|-------------------|-------------------|--------------|

|                 | iWrite (in)       | iRead (expected)  | TDO (OUT)    |

| init-data       | 0x54              | 0x13              | XX           |

## Mnemonics of course can be used as well

|           | iWrite (in) | iRead (expected) | TDO (OUT) |

|-----------|-------------|------------------|-----------|

| init-data | PCle        | Pass             | XX        |

iProc init\_setup is used to configure instance specific features of an IC.

Some init\_setup steps are consistent from one instance to another. - Ex: Turning PLLs off

Most likely all init\_run iProcs are exactly the same from one instance to another. Polling on a status bit for example

Several methods can exist to enable init\_setup which are shown in the following slides.

### Test Engineer generates settings from BSDL aware GUI

IP provided init\_setup for IO. Parameters passed in - not practical for 1000 I/O with four parameters each

iProc init\_setup { Proto Swing} {

iWrite Proto \$Proto

iWrite Swing \$Swing

iApply

iMatchLoop -begin

iRead Status Ready

iApply

iMatchLoop -end

}

For optimization some merging would help when this init\_setup is called at a higher level

## IP or IC provided init\_setup for IO. Parameters passed in for all I/O??? - not practical for 1000 I/O with multiple parameters each

iProc init\_setup { IO1\_Proto IO1\_Swing IO2\_Proto IO2\_Swing IO3\_Proto IO3\_Swing IO4\_Proto IO4\_Swing \ IO5\_Proto IO5\_Swing IO6\_Proto IO6\_Swing IO7\_Proto IO7\_Swing IO8\_Proto IO8\_Swing \

••••

IO998\_Proto IO998\_Swing IO999\_Proto IO999\_Swing IO1000\_Proto IO1000\_Swing } {

iWrite IO1 Proto \$IO1 Proto iWrite IO1 Swing \$IO1 Swing iWrite IO2 Proto \$IO2 Proto ;# PCIe, SATA, SRIO iWrite IO2 Swing \$IO2 Swing ;# 200mv 300mv 500mv 800mv iWrite IO3\_Proto \$IO3\_Proto iWrite IO3 Swing \$IO3 Swing iWrite IO4\_Proto \$IO4\_Proto iWrite IO4 Swing \$IO4 Swing iWrite IO5 Proto \$IO5 Proto iWrite IO5\_Swing \$IO5\_Swing iWrite IO6 Proto \$IO6 Proto iWrite IO6 Swing \$IO6 Swing iWrite IO7 Proto \$IO7 Proto iWrite IO7 Swing \$IO7 Swing iWrite IO8 Proto \$IO8 Proto iWrite IO8 Swing \$IO8 Swing . <many pages later> iWrite IO999 Proto \$IO999 Proto iWrite IO999 Swing \$IO999 Swing iWrite IO1000 Proto \$IO1000 Proto iWrite IO100 Swing \$IO1000 Swing iApply iMatchLoop -begin iRead Status Ready iApply iMatchLoop -end

Large ICs can benefit from PDL1

- description is compact, still recorded out as flat binary tester commands

- IC vendor supplied init\_setup

- what are the reasons we would not enable this?

```

iProc init setup { } {

set i 0 ;# variable

while { $i < 988 } {

iWrite IO($i).Pullup ON ; # register field

iWrite IO($i).ACMODE OFF ;# use DC I/O only

iWrite IO($i).WEN ON

incr i

}

iApply

}

```

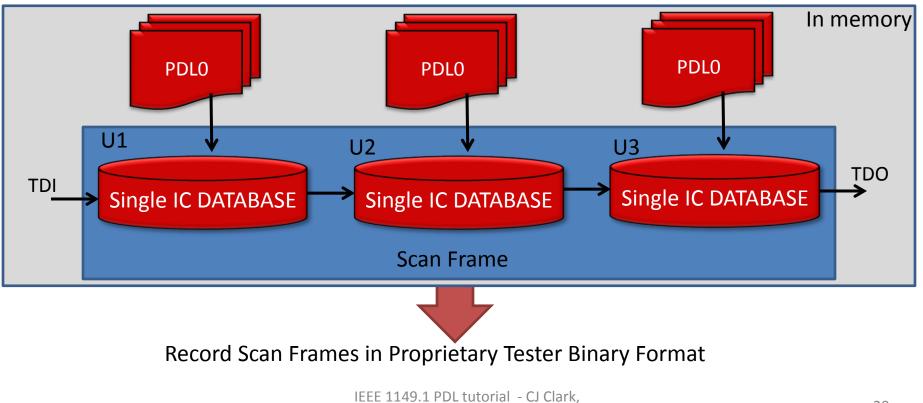

PULLUP, ACMODE and WEN are registers Register\_assembly supports arrays of I/O. Each PDL routine may be executed sequentially

- must stop at iApply (leave in interpreter)

- execute next PDL

- At 'last' PDL perform iApply

- continue with first PDL

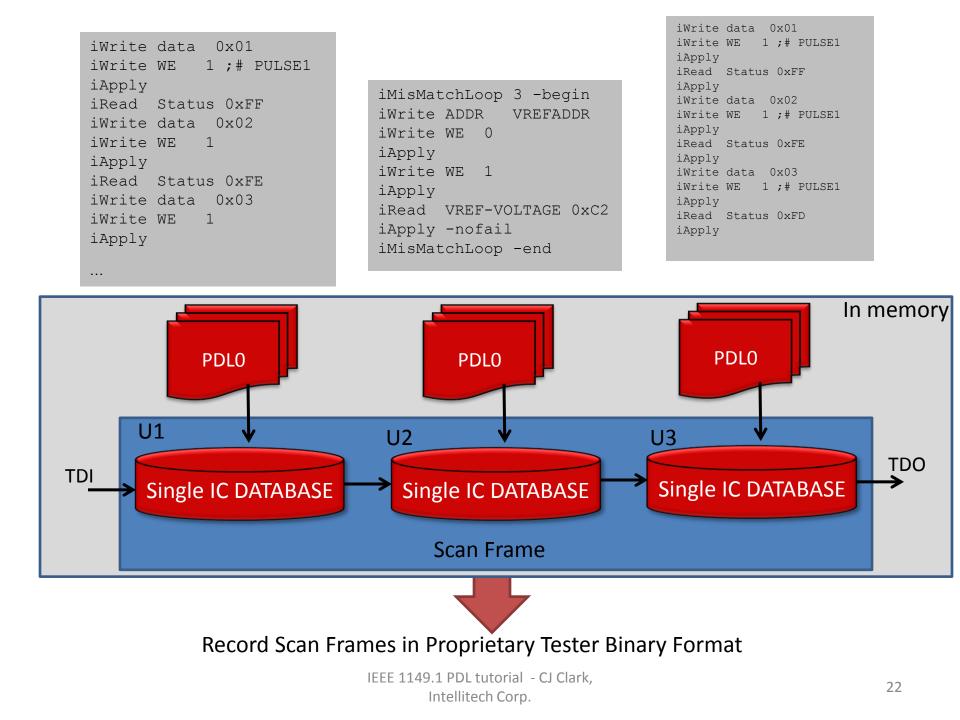

Various optimizations Available to vendor Such as slicing board Scan frame, then piecing In tester format

Record Scan Frames in Proprietary Tester Binary Format

(record separately register names/info tags as you wish for 'simple' diagnostics)

If one PDL ends before the others, then the scan frame data repeats -For discussion: 'merging' is not 'on' by default – hence the iMerge command Consider for init setup or init run iProc some may want it to be the default IEEE 1149.1 PDL tutorial - CJ Clark,

Intellitech Corp.

# Use Models

PDL0 iProcs

Designed for use with tester hardware

- memory behind pin, sequencer type with stim/exp/mask "load and go" type operation

For use in Production or Field where database of BSDL info is not coupled to Test application.

High-speed - hardware comparison - TDO data is compared with expected and masked by X bits

iProcs init\_setup, init\_run could be defined as PDLO only (potentially)

(some may view this as challenging and would like

the ability to use PDL1 to describe init\_setup)

```

# A PDL File for IC vendor XYZ's ABCIC would be as follows :

iPDLLevel 0 -version IEEE1149 1 2012 ; # level-0 PDL only

iProcGroup ABCIC ;# entity or package name -iProcTarget

iProc init setup { param } {

iWrite Corel PLL1 $param ;# REGISTER FIELD

iWrite Corel PLL2 $param

iWrite Core2 PLL1 $param

iWrite Core2 PLL2 $param

iWrite Reg ON ;# triggers just from a DR scan

iWrite RegEN ON ;#

iApply

iWrite RegEN OFF ;# required to leave init setup in non-triggered mode

iApply

}

# this is the same for all ABCIC's

iProc init run {} {

In memory:

iRunLoop 10000 ; # 10,000 TCK cycle delay

iRead init status(1) Pass

iApply

ABCIC.init setup

ABCIC.init run

}

ABCIC.main

# this is the same for all ABCIC's

iProc main {} {

ABCIC.userdefined

iProc userdefined {} {

}

IEEE 1149.1 PDL tutorial - CJ Clark,

# EOF

```

P1687 and 1149.1

iCall U3.init\_setup

(look up u3 what it is (ABCIC) And then call the iProc Associated with it In the context of U3.) iRead U3.init\_status(1) iWrite U3.Core1\_PLL1 In memory:

ABCIC.main ABCIC.userdefined ABCIC.init\_setup ABCIC.init\_run Tool is seeing:

| iWrite | U3.Core1             | PLL1 | OFF |

|--------|----------------------|------|-----|

| iWrite | U3.Core1<br>U3.Core2 | PLL2 | OFF |

| iWrite | U3.Core2             | PLL1 | OFF |

| iWrite | U3.Core2             | PLL2 | OFF |

Strip proc name off, look up instance path type <entity or package file> Pass the <instance path> to the proc formed by <entity or package file>.proc

```

iPDLLevel 0 -version STD IEEE 1149 1 2012

iProcGroup U3 ; # Associate the following procs with U3

# this procedure becomes U3.init setup internally to the PDL

interpreter

iProc init setup { } {

U3.init setup

;# call IC vendor init setup

iWrite Clock 125Mhz ; # use of BSDL mnemonics

iWrite Voltage 0x40 ; # use of hex values

iWrite Protocol PCIe

; # use of BSDL mnemonics

iApply

Probably no

iProc main {} {

U3.main

;# call on chip tests xyz

#U3.membist

;# tool generates this commented out

;# test engineers enable

#end of file

Also In memory:

In memory: U3.init setup

U3.main

ABCIC.init setup

ABCIC.init run

ABCIC.main

```

### ABCIC.userdefined

IEEE 1149.1 PDL tutorial - CJ Clark. Intellitech Corp.

way to automate everything. Test engineers will still have jobs

1149.1 Same. Operation. (Drop iTarget). However

- note loss of knowing type

- solution? Easier to use instance names has been suggested

iCall U3.main ;# call instance U3 or ABCIC main?????? iCall U3.init\_setup ;# call instance U3 or ABCIC init\_setup?????

Why -direct here? (parameters come after iProc)

> iCall –direct U3.main iCall U3.main iCall U3.init\_setup iCall -direct U3.init\_setup

;# call it directly no lookup

;# call prebuilt init\_setup for ABCIC

; # call instance specific init\_setup

In memory: U3.init\_setup U3.main Also In memory:

ABCIC.init\_setup ABCIC.init\_run ABCIC.main ABCIC.userdefined 1149.1 Are init\_setup by default Merged? up to tool vendor to merge or not merge init\_setup?

init\_run MUST be merged in WG current collective thinking

iCall U3.init\_setup iCall -direct U3.init\_setup ;# call prebuilt init\_setup for ABCIC

; # call instance specific init\_setup

Can this be done to reduce?

iMerge -begin ; # reduce iApply iCall U3.init\_setup iCall -direct U3.init\_setup iMerge -end

In memory: U3.init\_setup U3.main Also In memory:

ABCIC.init\_setup ABCIC.init\_run ABCIC.main ABCIC.userdefined

IEEE 1149.1 PDL tutoria

Intellitech Corp.

iLoop/iUntil Loop in an iProc for U2?

- record the loop start in tester binary format, max count

- process U1 and U3 as usual

- continue to next iApply (other choices don't seem to work

- load same frame data repeatedly, clear expected data (XXX) on U1/U3 scan frame)

- record same frame data only on PDL which ends for U1 and U3

- any PULSE1/PULSE0 cells which take on 1 after 0 must be set back after iApply

- record end in tester binary format

- resume recording round-robin on each PDL/iProc

iLoop/iUntil - two examples in draft - used for 'rdy' or 'bsy' type polling - tools can merge or not merge as they see fit (not possible for init run) - iLoop can 'block' and other procs would finish before loop section iProc XYZ EXIO {} { # external voltage may be coming up or non-stable get # 10 good readings before proceeding otherwise remaining tests may # have failures due to instability iLoop -begin ;# repeat iWrite ADDR VREFADDR iWrite WE 0 iApply iWrite WE 1 ;# register dump from OS iApply iRead VREF-VOLTAGE 0xC2 ;# Loop to make sure VREF is stable Error if any reading is incorrect ;# iApply -nofail iUntil -match #; VREF stable This is currently an 'implied -nofail' } (All iApply inside) suggest

iApply -nofail on appropriate ones

iMatchLoop/iMisMatchLoop

- -Tool responsible for optimization (if any)

- Tool can simply stop at iM/iMM commands and finish other iProcs

- Tool can continue to merge (standard is silent on this)

- -Tool responsible for practical limits (maxcnt = 999999?)

- -Note in U3, PULSE1 being reset to 0 to match cell return to 0

- -PDL writers always need to verify/don't end in triggering states

- -Tool can simply take diminutive case of maxcnt = 1

- -Tool responsible for exiting on failures/register dumps etc as desired

|      | U1     |    |          | U2      |          |      | U      | 3   |                  |

|------|--------|----|----------|---------|----------|------|--------|-----|------------------|

| Data | Status | WE | ADDR     | WE VREF | -VOLTAGE | Data | Status | WE  |                  |

| 0x01 | хх     | 1  | VREFADDR | 0       | ХХ       | 0x01 | XX     | 1   |                  |

| 0x02 | OxFF   | 1  | VREFADDR | 1       | ХХ       | 0x01 | OxFF   | 0 🧲 | automatic return |

| 0x03 | OxFE   | 1  | VREFADDR | 1       | 0XC2     | 0x02 | XX     | 1   | to 0 for         |

| 0x04 | 0xFD   | 1  | VREFADDR | 0       | ХХ       | 0x02 | OXFE   | 0   | WE on<br>iApply  |

| 0x05 | 0xFC   | 1  | VREFADDR | 1       | ХХ       | 0x03 | XX     | 1   | without          |

| 0x06 | OxFB   | 1  | VREFADDR | 1       | 0XC2     | 0x03 | 0XFD   | 0   | iWrite WE        |

| 0x07 | 0XFA   | 1  | VREFADDR | 0       | ХХ       | 0x04 | XX     | 1   |                  |

| 0x08 | 0XF9   | 1  | VREFADDR | 1       | ХХ       | 0x04 | OXFC   | 0   |                  |

| 0x09 | 0xF8   | 1  | VREFADDR | 1       | 0XC2     | 0x05 | xx     | 1   |                  |

|      |        |    |          |         |          |      |        |     |                  |

explicit enable for WE on each iApply

PDL<sup>EEE</sup> 11491 PDL<sup>t</sup> into tester binary format

ifTrue/ifFalse - High-speed flow control

- -Branching based on miscompare/compare of expected data

- -Carol's pins need a check and exit (tester stop-on-fail is not guaranteed to be on)

- simple example, ignore argument on how many different package files and PDL can be delivered as an alternative that is not scalable and requires more integration at top level

Multiple file solution doesn't work around problem that production may have three or four versions of IP in production line or in field across multiple ICs. We'd like the IP to deal with its own init\_setup variations to lower the downstream costs

```

iProc INIT SETUP {} {

iRead VERSION 0b01

iApply -nofail

;# tell tester OS not to dump register

;# The first version uses TERM1

ifTrue

iWrite SWING 800mv

iWrite CMMV Test cm

iWrite UPD

ON

iWrite TERM1 Test

iApply

:# Version 2 the bits are swizzled

ifFalse

;# max swing with this rev

iWrite SWING 600mv

iWrite CMMV Test cm

iWrite UPD

ON

iWrite TERM2 Test ; # set the bits differently on this rev

iApply

ifEnd

```

```

iWrite UPD OFF ;# prevents further updates

} IEEE 1149.1 PDL tutorial - CJ Clark,

Intellitech Corp.

```

# ifTrue/ifFalse - High-speed flow control - need to set failure in some cases

iProc INIT SETUP {} { iRead Observe IO VSEL 0x13 ;# observe Freescale's strapping pins (5 bit value) iApply -nofail ifFalse ;# catastrophic iWrite myreg -safe ;# example of setting value before failing/exiting iApply iSetFail -quit ; #all bets off, we need to tell tester to exit ifTrue iWrite xxxx iApply iRead xxxx iApply ifEnd

}

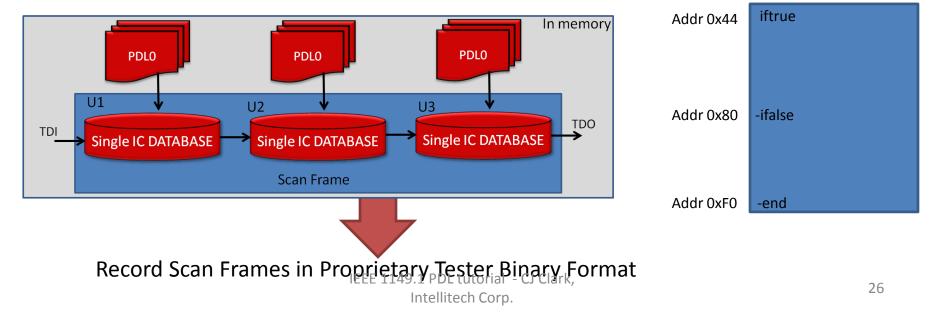

ifTrue/ifFalse/ifEnd

- Record both ifTrue and ifFalse

- record command in tester format to "-nofail" on first iApply

- record iApply

- One option: Stop processing U1/U3 (there are some optimizations available) choices: load same frame data on U2's iApply and optionally clear expected data (XXX) on U1/U3 scan frame

a) PULSE1/PULSE0 cells which take on 1 after 0 must be set

- record tester's binary command for branch-on-compare/miscompare (branch address set when else and end command encountered)

- record scan frames for If, record tester binary command for else compare

- record scan frames for else

- record/set -- end location + 1 for branch operations

#### **Tester Memory**

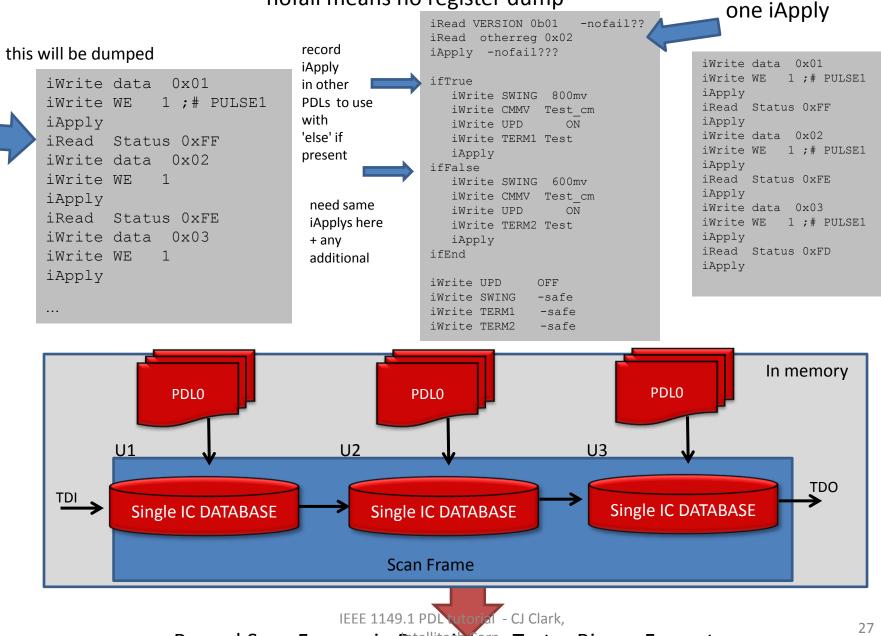

# Piece binary iApply together for U1/U3 for both ifTrue/ifFalse - nofail means no register dump

Record Scan Frames in Proprietary Tester Binary Format

### Recorded test binary format for both the ifTrue and the ifFalse

- tester has to have command to branch on miscompare with addr

- tester needs Jump command at ifFalse to jump over ifFalse

- when iftrue/iffalse/ifend is non-symmetric, tool needs to align

|       |       |    | Data | Status | WE | VERSION | SWING | CMMV    | UPD | Term1      | Term2      | Data | Status | WE |

|-------|-------|----|------|--------|----|---------|-------|---------|-----|------------|------------|------|--------|----|

|       |       | 1  | 0x01 | XX     | 1  | хх      | safe  | safe    | OFF | safe       | safe       | 0x01 | ХХ     | 1  |

| check | BNE 4 | 2  | 0x02 | 0xFF   | 1  | 0b01    | safe  | safe    | OFF | safe       | safe       | 0x01 | 0xFF   | 0  |

| TRUE  | JMP 5 | 3  | 0x03 | 0xFE   | 1  | хх      | 800mv | test_cm | ON  | test       | (swizzled) | 0x02 | ХХ     | 1  |

| FALSE |       | 4  | 0x03 | 0xFE   | 1  | хх      | 600mv | test cm |     | (swizzled) | test       | 0x02 | XX     | 1  |

| end   |       | 5  | 0x04 | 0xFD   | 1  | хх      | safe  | test_cm |     | safe       | safe       | 0x02 | OXFE   | 0  |

| chu   |       | 6  | 0x05 | 0xFC   | 1  | xx      | safe  | test_cm |     | safe       | safe       | 0x03 | XX     | 1  |

|       |       |    |      |        |    |         |       | _       |     |            |            |      |        |    |

|       |       | 7  | 0x06 | OxFB   | 1  | XX      | safe  | test_cm |     | safe       | safe       | 0x03 | 0XFD   | 0  |

|       |       | 8  | 0x07 | OXFA   | 1  | XX      | safe  | test_cm | OFF | safe       | safe       | 0x04 | XX     | 1  |

|       |       | 9  | 0x08 | 0XF9   | 1  | XX      | safe  | test_cm | OFF | safe       | safe       | 0x04 | 0XFC   | 0  |

|       |       | 10 | 0x09 | 0xF8   | 1  | хх      | safe  | test_cm | OFF | safe       | safe       | 0x05 | XX     | 1  |

```

User developed INIT_SETUP iProc for an instance U3

-No IP provided init setup iProc

-Since init setup/init run are pre-defined possible to

have them 'iExported' by default

iPDLLevel 0 -version STD IEEE 1149 1 2012 ; # level-0 PDL only

iProcTarget U3 ; # Associate the following procs with the instance of U3

; # indicate to user/tools these procs available

iExport

# this procedure becomes U3.init setup internally to the PDL interpreter

iProc init setup {} {

iPrefix i1

iWrite Clock 125Mhz

; # use of BSDL mnemonics

iWrite Voltage 0x40 ; # use of hex values

iWrite Protocol PCIe

; # use of BSDL mnemonics

iApply

}

# this procedure becomes U3.init setup internally to the PDL interpreter

iProc init run {} {

iRunLoop 10000 ;

# 10,000 TCK cycle delay

iPrefix i1

iRead init status(1) Pass; # use of single register bit

iApply

}

#end of file

```

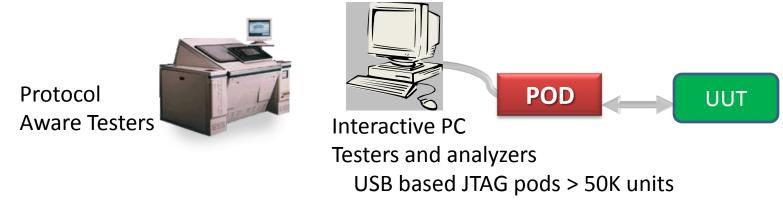

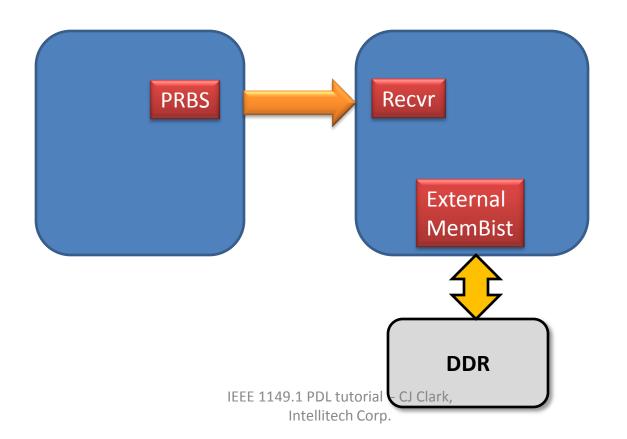

Other use models of 1149.1

- 1149.1 is used in non-production segments of the industry

### Interactive mode:

IC Characterization, Debug, lab bring up, system analysis, IC to IC SERDES testing, IC to DDR memory testing, Working With mixed signal devices (DACs and ADCs), voltage reading, temperature reading, read-write-modify registers.

This mode requires use of iGET on -SO (return) data.

#### 1. Overview

#### 1.1 Scope

This standard defines test logic that can be included in an integrated circuit to provide standardized approaches to

- testing the interconnections between integrated circuits once they have been assembled onto a printed circuit board or other substrate;

- testing the integrated circuit itself; and

- observing or modifying circuit activity during the component's normal operation.

What is PDL1?

PDL1 is these two commands (iGet and iGetStatus)

note addition of -FAIL from Friday's meeting

+ All PDL0 commands

+ TCL (Tool Command Language)

TCL has been around since late 1990s. Used in nearly all EDA tools, both major FPGA vendors use TCL.

### Table C-3—PDL Level-1 Commands

| iGet <register>         [-IN   -OUT   -EXPECT   -FAIL]         [-HEX   -BIN   -DEC   -MNEM]       Return a TCL string representing the value associated with a register in the specified format.         iGetStatus       [-clear]       Get the pass/fail status since the last</register> | Command    | Parameters                     | Purpose                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------|-----------------------------------------|

| iGetStatus [-clear] Get the pass/fail status since the last                                                                                                                                                                                                                                 | iGet       | [-IN   -OUT   -EXPECT   -FAIL] | value associated with a register in the |

|                                                                                                                                                                                                                                                                                             | iGetStatus | [-clear]                       | Get the pass/fail status since the last |

| time it was eleared.                                                                                                                                                                                                                                                                        |            |                                | time it was eleared.                    |

13176

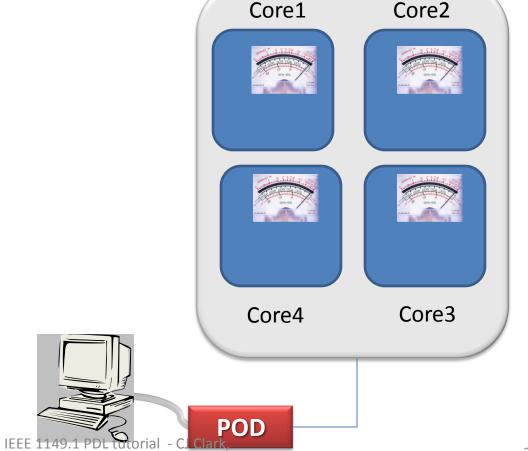

Safe and cool - how do we know? PDLO only checks EXPECTED values. Not suitable for setting a range or < less than or > greater than as all those values are not the expected - can be used in 3D-SIC stacks as well.

# vendor supplied reg to temp conversion

proc Reg2Temp { \$regval \$CorF } {

```

...

Core1

Core2

iExport -begin

# this proc returns a temperature and

# high level warnings could be specified

iProc init-setup-temp-check { } {

iRead tempreg

iApply

set val [iGet tempreg]

# convert reg value to temperature in celsius

set temp [Reg2Temp $val CEL]

#if {temp > 70} {

Core4

Core3

#puts "Temperature is excessive $temp"

#}

return temp

}

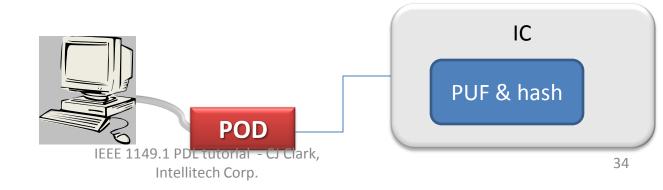

POD

IEEE 1149.1 PDL tutoriai - CJ Cla

Intellitech Corp.

```

AVS - automatic voltage scaling. Monitor mission mode operation during characterization. While CPU can access voltage monitors, if software is not prepared, 1149.1 is a convenient access mechanism to monitor AVS during bring-up, functional test (idea from Dharma)

# this proc returns a temperature and # high level warnings could be specified proc Reg2voltage {} {

}

iExport -begin

iProc read-voltage{ } {

iRead voltagereg

iApply

set val [iGet voltagreg]

# convert reg value to voltage

set volts [Reg2voltage \$val]

return volts

}

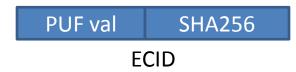

Counterfeit parts continue to be a very well known problem

## - ECID may not be just a 'value' to program in or to read out

Subject: Global IC and Hong Dark Suspect Counterfeit Electronic Parts

recent letter from DoD contractors to suppliers The attached correspondence from the United States Air Force indicates that Hong Dark Electronic Trade Company a/k/a Hong Dark Electronic Co., Ltd. a/k/a Hong Dark Electronics Co., Ltd. a/k/a Hongdark Electronic Co., Ltd. a/k/a Hongdark Electronics Co., Ltd. a/k/a Shenzhen Hongdark Electronics Co., Ltd. a/k/a Hongdark Electronic a/k/a Hongdark Technology Co., Limited a/k/a Hongdark a/k/a Hong Xing Da Technology Co., Ltd. (collectively Hong Dark), Global IC Trading Group, Inc., and Global IC Trading Group, LLC (collectively Global IC) have been suspended from government contracting and from directly or indirectly receiving the benefits of federal assistance programs. In order for us to assess the impact of any potential counterfeit parts in our products,

## 1149.1 ECID can help!

## PUF = physically unclonable function (layout dependent) SHA256 = Secure Hash Algorithm

Counterfeit parts continue to be a very well known problem

- ECID may not be just a 'value' to read out.

```

PUF val

SHA256

iPDLLevel 1 -version STD IEEE 1149 1 2012

iProcGroup MNO ECID V1 ; # Associate the following procs MNO's ECID

# this is a SHA256 on the ECID read value with

iProc SHA256Calc { data } {

;# too many details to show but needs PDL1

. . .

;# perhaps even external program call

}

# this procedure reads MNO company's ECID IP

iProc ECID {}

{ }

iRead ECIDREADDONE 1

iRead ECIDPUF

iRead ECID Hash

#iRead ECID WaferNum

IC vendor may not want to describe these

#iRead ECID DieNum

registers (optional)

#iRead ECID ManuLocation

iApply

set data [iGet ECIDPUF]

set ECIDHash [iGet ECID HASH]

set hashval [SHA256Calc $data]

if {$hashval != $ECIDHash} {

puts "ERROR: Read Hash Does Not Match Expected - Exp: ECIDHash, Act:$hashval\n"

}

#this information may or may not get released

# they are just numbers, so without a decoder ring, the data is

# meaningless to end users

[iGet ECID WaferNum D]

set WaferNum

[iGet ECID DieNum D]

set DieNum

set ManuLocation [iGet ECID_ManuLocation]

IEEE 1149.1 PDL tutorial - CJ Clark,

Intellitech Corp.

```

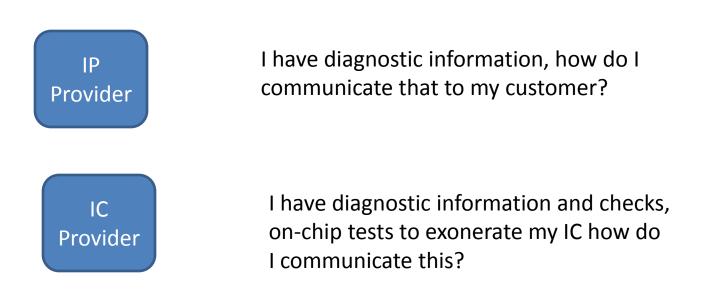

iProc allow additional routines from IC vendor for checking - PDL1 used as a description language for constraints

```

iPDLLevel 1

iExport -begin

iProc check-values {} {

set val1 [iGet -IN -MNEM swing] ; # 200mv, 400mv 800mv

set val2 [iGet -IN -MNEM protocol] ; # PCIe, SATA

if { $val1 == "200mv" && $val2 == "SRIO" } {

puts "The I/O can not be set to 200mv in SRIO mode"

return FALSE; # instruct tool that check failed

}

```

}

### 1.1 Scope

This standard defines test logic that can be included in an integrated circuit to provide standardized approaches to

- testing the interconnections between integrated circuits once they have been assembled onto a printed circuit board or other substrate;

Some tests cannot easily be described in PDL0 - some failing bits in SERDES test are tolerated DDR memory tests, while slow speed tests can be done through EXTEST, less faults can be detected and test time can be unacceptable

PDL0 Diagnostics:

- Register: DATA expected 0x55 received 0x40

Without a common language we have classic tower of Babel

# IEEE 1801 extends TCL with commands for describing power intent - very much in alignment with this proposal

6.5.2 errorInfo

-P1687 potentially will include some form of PDL1

See the Tcl command reference [B5].

### 6.6 add\_domain\_elements

| Purpose         | Add design elements to a power domain                     |                                                                                                                                                                             |  |

|-----------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax          | add_domain_elements domain_name<br>-elements element_list |                                                                                                                                                                             |  |

|                 | domain_name                                               | The power domain to modify.                                                                                                                                                 |  |

| Arguments       | -elements element_list                                    | The list of design elements to add. The elements shall be referenced relative<br>to the active scope and are the descendents of the scope of the specified<br>power domain. |  |

| Return<br>value | Return a 1 if successful or raise a TCL_ERROR if not.     |                                                                                                                                                                             |  |

The add\_domain\_elements command provides the ability to separate the creation of a power domain from the specification of the elements contained within it. This is similar to only specifying the elements using the -elements option in the create\_power\_domain command (see <u>6.19</u>). The effect of add\_domain\_elements is additive, i.e., a power domain consists of any elements specified in the create\_power\_domain command and those elements specified in any add\_domain\_elements commands.

It shall be an error if domain\_name does not indicate a previously created power domain.

#### This command is semantically equivalent to

where any *italicized* arguments are implementation-defined.

Possible syntax errors did not prevent the adoption of TCL in that standard - TCL like BSDL ( or verilog) has to be verified IEEE 1801's entire syntax reference points to TCL links in an informative annex bibliography - precedence that we don't have to include all syntax in 1149.1, just the syntax of 1149.1 commands

Annex A

(informative)

## Bibliography

[B1] IEEE 100, *The Authoritative Dictionary of IEEE Standards Terms,* Seventh Edition. New York: Institute of Electrical and Electronics Engineers, Inc.

[B2] IEEE Std 1364<sup>™</sup>, IEEE Standard for Verilog Hardware Description Language.<sup>7</sup>

[B3] ISO/IEC 8859-1, Information technology—8-bit single-byte coded graphic character sets—Part 1: Latin Alphabet No. 1.<sup>8</sup>

[B4] For a summary of Tcl language syntax, see the following Internet location: <u>http://www.tcl.tk/man/tcl8.4/TclCmd</u>.

[B5] For more details on using the Tcl language, see the following Internet location: <u>http://sourceforge.net/projects/tcl/</u>.

[B6] For more details on using the Liberty library format, see the following Internet location: <u>http://synopsys.com/cgi-bin/tapin/login1.cgi</u>.

[B7] Coding examples are available from the UPF *WG* World Wide Web site <u>http://www.accellera.org/upf/</u>references.html.

### iGet command is liked so much it was "brought" to P1687 before 1149.1 has voted

----Original Message-----From: Ted (Theodore) Eaton-SSI [mailto:t.eaton@ssi.samsung.com] Sent: Wednesday, February 08, 2012 10:37 PM To: Rearick, Jeff; hugh wallace@agilent.com; acrouch@asset-intertech.com; bill.bruce@siliconaid.com; Brian Turmelle; hojun@cisco.com; Doege, Jason; jeffrey wilkerson@non.agilent.com; JF Cote@mentor.com; Jpotter@asset-intertech.com; Martin Keim@mentor.com; mcoldewey@asset-intertech.com; mlaisne@OUALCOMM.COM; szuo@OUALCOMM.COM; teaton@ieee.org; CJ Clark; carl.barnhart@SILICONAID.COM Cc: ken.posse@avagotech.com Subject: RE: Draft Chapter 8 All, Here is the iGet command definition from the current 1149.1 draft for consideration. iGet <register> [IN | OUT | EXPECT] [HEX | BIN | DEC | MNEM] Return a TCL string representing the value associated with a register in the specified radix. My Thoughts : The default behavior of the PDL1 commands seems to be targeted for a 1. specific tester type. From my standpoint, most environments and PDL will be most interested in seeing the results of the previous iApply rather than a history of the last N iApply operations. It seems to me that it would be better for the iGet<\*> commands to default to : Capture Active (the data of the last operation is available without a. the use of iCaptureData). iGetReadValues returns the result of the last iApply for a register. a. (does these need to be the last iRead-iApply sequence, not sure). b. iGetWriteValues returns that value of the last iWrite command to that register iGetExpectValues returns the value of the last iRead command to that c. register i. If the last iRead did not have an expected value an X value is returned ii. If an iApply has been performed after the iRead, what is returned . Expect data is not sticky so I would assume the current state of the registers expect data is X Capture depth is 1 by default. b. 2. The Radix of the return value is not defined here. It seems that we should have some switch/parameter available to allow the user to select a Radix (BIN/HEX/mnemonic/INT?) 1149.1 has a similar process defined that seems more compact and may 3. be a good place that we can consolidate ( I will provide the exact command specification when I get access) We can leave the iCaptureData function available for memory behind. 4. pin or other testers that can make use of a pattern buffer history, but the default behavior would be defined as above.  $A_{1}$ Intellitech Corp.

| Register_fields are just pointers to bits. iWrite mysinglebit 0 |             |                  |           |  |  |  |  |  |

|-----------------------------------------------------------------|-------------|------------------|-----------|--|--|--|--|--|

|                                                                 | iWrite (in) | iRead (expected) | TDO (OUT) |  |  |  |  |  |

| init-data                                                       | 0x54        | 0x13             | XX        |  |  |  |  |  |

| Mnemonics of course can be used as well                         |             |                  |           |  |  |  |  |  |

|           | iWrite (in) | iRead (expected) | TDO (OUT) |

|-----------|-------------|------------------|-----------|

| init-data | PCIe        | Pass             | XX        |

iGet returns data from each of the three fields.

set val2 [iGet -EXP -MNEM init-data] set val2 [iGet -EXP -MNEM init-data] set val3 [iGet -OUT -HEX init-data] set val4 [iGet -FAIL -BIN init-data] puts "\$val \$val2 \$val3 \$val4" - output: PCle Pass 0xXX 0bXXXXXXX For discussion: PDL1 ends up not being much different - Consider iGet -OUT <regname> as non-merge-able - iGet -IN and -EXP data *is* merge-able -Requires use of TCL interpreter -Instead of private compiler of PDL0 -math, expressions/branching all resolve into an iApply on a populated scan frame

IEEE 1149.1 PDL tutorial - CJ Clark, Intellitech Corp.

## For consideration: Constraints can be described directly in PDL1

```

# default value is 'off' for param check

iProc Constraints { { check OFF } } {

if { $check == ON } {

set val1 [iGet -IN -MNEM DOMSELA] ; # DOM A ON

set val2 [iGet -IN -MNEM DOMSELB] ; # DOM B ON

if { $val1 == "ON" && $val2 == "ON" } {

puts "ERROR Domain A cannot be turned on when Domain B is on"

iWrite DOMSELA OFF

return FALSE ;# instruct tool init setup failed

}

}

return TRUE;

}

```

It does appear 'sequential' or 'executable' but the approach is essentially a More robust form of the BSDL constraint attribute. Without the need for The WG to create a language inside of BSDL

IEEE 1149.1 PDL tutorial - CJ Clark, Intellitech Corp. One approach which has been used in the past

```

attribute REGISTER_CONSTRAINTS of mychip : entity is

"(DOMAINA == ON && DOMAINB == ON)";

```

```

Need a language for operators: X % ! + - /

```

And order precedence ()

- note we have just two registers, what about 3 or 4 or 10?

What about?

attribute REGISTER\_CONSTRAINTS of mychip : entity is "(REGA + 1 && REGB)"; ;# math required

Sequential constraints REGA can't be a 1 after being a 0 and REGB is a 0? BSDL is a difficult place to describe these relationships

What happens when constraints not met? What is the error message?

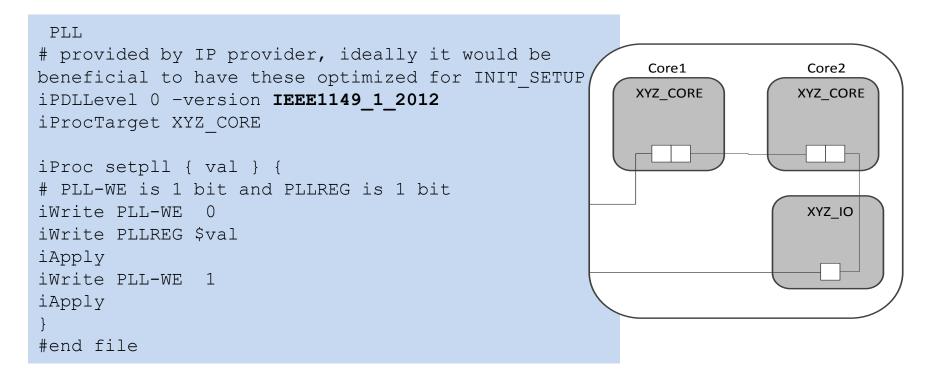

Merging with iMerge

Merging – used for reducing scan operations

```

iPDLLevel 0 -version IEEE1149_1_2012 ; # level-0 PDL only

iProcTarget XYZ_IO

iProc init_setup { val } {

iWrite AC-MODE $val

iApply

}

#end file

```

iMerge Discussion: Are iCalls merged automatically in init\_setup or init\_run?

```

iPDLLevel 0 -version IEEE1149_1_2012

iSource XYZ_CORE.PDL

iSource XYZ_IO.PDL

iProcTarget XYZOxygen

```

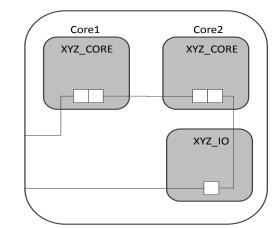

iProc init\_setup { } {

iMerge -begin

iCall U1.Core1.setpll OFF ;# XYZ\_CORE two iApply

iCall U1.Core2.setpll OFF ;# XYZ\_CORE two iApply

iCall U1.i1.init\_setup OFF ;# XYZ\_IO one iApply

iMerge -end

}

#end of file

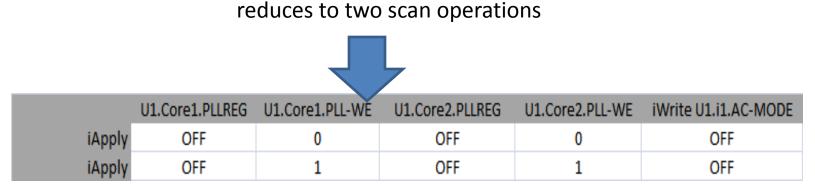

## PLL vendor does not know where PLL is in final IC

Like board level Scan Path Linkers, tool is responsible for opening SEGSELs, turning on DOMCTRL

Checking for OO on Power pins and SEGSEL captures are catastrophic events which a tool can know during tester binary format recording and insert proper tester command # IP iProc init\_setup {} { iWrite PLL OFF iApply }

This adds to work for end user: iWrite s1 ON iApply iCall PLL1.init\_setup

Tool manages access to TDR Potentially in one iApply this is done iApply is :

IR scan if required

DR to turn on Domains (if any)

observe DOM\_EXT SEGSELs

DR - to open/capture power

on internal power domains

DR - to PLL