# **WDM PICs for Optical Interfaces**

**Integrated Photonics for 100G Interfaces**

IEEE Next Gen Optics, 2012 Jul 16-20

## Contributors and Supporters

#### **Contributors:**

- Randy Perrie (OneChip)

- Andy Weirich (OneChip)

- Valery Tolstikhin (OneChip)

- Fang Wu (OneChip)

#### **Supporters:**

- Arlon Martin (Kotura)

- Samir Desai (Kotura)

- Mehdi Asghari (Kotura)

# Why Integrate?

- History of electronics shows that integration reduces cost

- Reduces manual assembly cost

- Improves manufacturing yield and uniformity

- Improves robustness

- Functions that are presently expensive benefit most from future cost reduction through integration

- Computers were once expensive, are now pervasive and cheap... and even contained in the least expensive PON transceivers

- The largest future cost reduction due to integration will likely be enjoyed by more feature-rich blocks, e.g. WDM vs. single-λ interface

# Photonic Integrated Circuits (PICs)

- Much has been presented to the Task Force about using PIC architectures:

- Palkert\_01\_1111

- 2. Palkert\_01c\_0312

- 3. Palkert\_02b\_0312

- 4. Palkert\_03b\_0312

- 5. Palkert\_01\_0512

- To date, the predominant architecture presented has been a parallel fiber architecture utilizing silicon photonics.

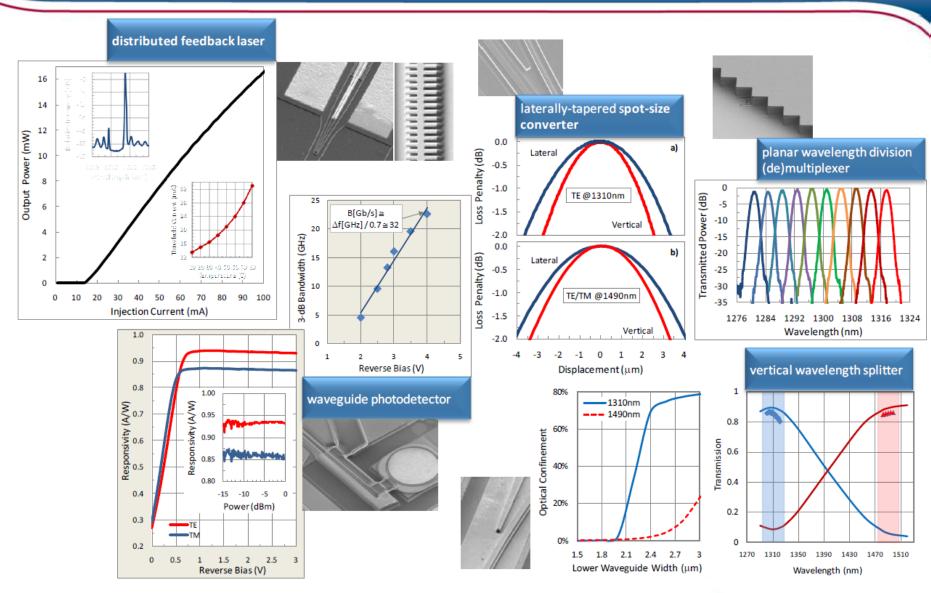

#### PIC structures in InP

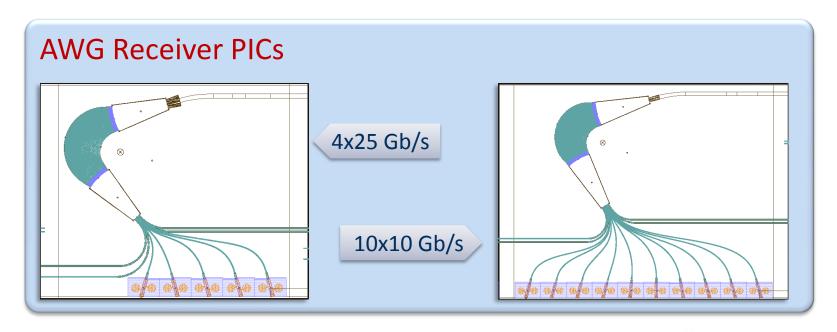

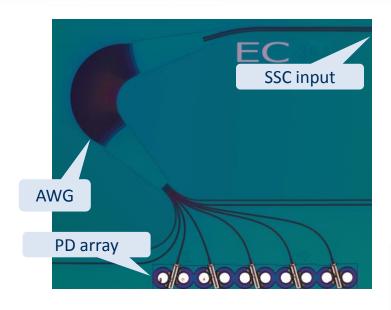

### WDM PICs

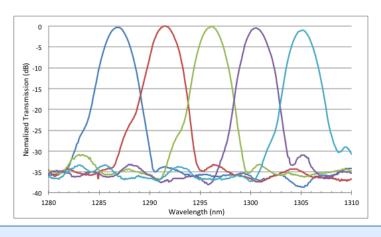

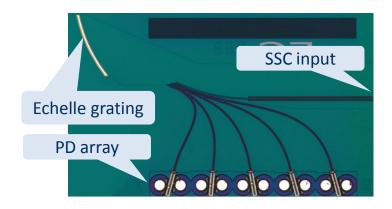

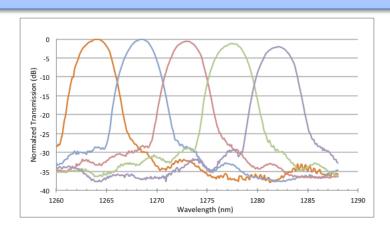

Providing multi-channel WDM functionality in planar devices has been well-demonstrated in the industry using either Arrayed Waveguide Grating or Echelle Grating structures.

### WDM Receiver PICs

#### Key performance features

- FC responsivity: 0.25 A/W

- Adjacent (non-adjacent) xtalk: -30 dB (-35 dB)

- Polarization dependent λ (FC responsivity): 0.03 nm (0.3 dB)

- 3-dB BW: 21 GHz (>25 GHz in Phase 2)

# WDM PICs

| IC (CMOS)                                                                                                                               | PIC (MGVI)                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Standard</b> material: Si/SiO <sub>2</sub>                                                                                           | Material: InP and related compound semiconductors on Fe:InP substrate                                                                     |

| Standard device design / processing                                                                                                     | <b>Devices</b> : design / fabrication building blocks                                                                                     |

| <b>Standard</b> design rules for building the circuit out of individual devices                                                         | <b>Circuits</b> : functional integration – vertical, parallel integration – at the same vertical level                                    |

| <b>Standard</b> process flow and wafer fabrication steps                                                                                | <b>Fabrication</b> : generic processes, e.g. dry / wet etch, passivation, planarization, metallization                                    |

| <b>Standard</b> (s/w) design tools for converting the circuit design into photomasks compatible with standard fabrication process       | <b>Design tools:</b> some commercial (e.g. BPM) but mostly in-house, still long way to go towards automated computer-aided design toolset |

| <b>Standard</b> on-wafer testing techniques and procedures                                                                              | <b>Testing:</b> once PICs have on-chip active devices, automated wafer probing is a very real option                                      |

| Standard pin layout and packaging                                                                                                       | Packaging: application driven, on a Si bench                                                                                              |

| Fabless model that enables for ASIC design to<br>be decoupled from the device design at one<br>end and wafer fabrication – at the other | Fabless model that <i>potentially</i> allows for ASPIC design to be decoupled from both the device design and wafer fabrication           |

#### Conclusions

- End user comments (in palkert\_02b\_0312) that users are looking for the lowest cost connectivity solution:

- Medium sized data center: I don't like parallel fiber because I

have to carry spares in the data center, however, cost is

absolutely king and I will deploy the lowest cost technology.

- Very Large data center: I will deploy the lowest cost solution regardless of the fiber type. If PSM4 is not standardized I encourage the formation of an MSA outside the IEEE.

- Large MSO: We deploy only SMF in our data centers.

### Conclusions

- As noted in Kolesar\_01b\_0112 8-lane cabling is 4x to 5x more expensive than 2-lane cabling

- As noted in Kipp\_01\_0112 there is only a 20% cost premium nR4 (with WDM) versus nR4 (without WDM).

- The additional cost of parallel fiber in PSM4 will be greater than a WDM module implemented with PICs.

- A duplex fiber nR4 could be compatible with existing LR4 implementations.