## Google

# Technical Feasibility of Passive Copper Cables at 200Gbps/lane

Leesa Noujeim, Sara Zebian, and Hong Liu

IEEE 802.3 Beyond 400G Ethernet Study Group, May 17 2021 (r2)

- Motivations for 200Gbps per lane

- 200Gbps/lane electrical components readiness

- Link budgets for 200Gbps/lane

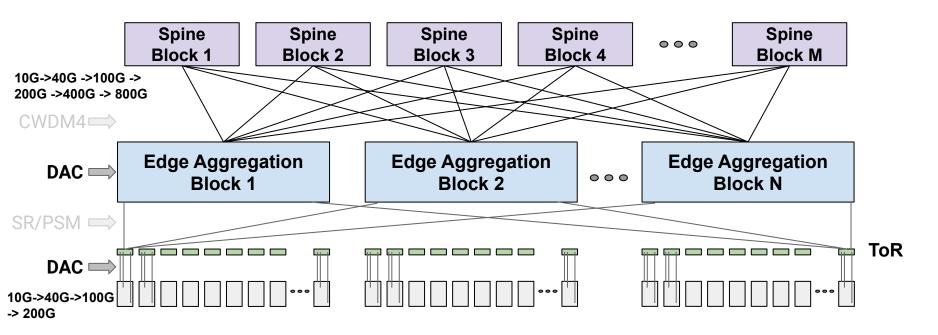

#### >400G will be needed in Datacenter Network fabrics

DAC (Direct Attach Copper) is the most efficient interconnect for edge block and TOR

#### Motivations for 200Gbps/lane

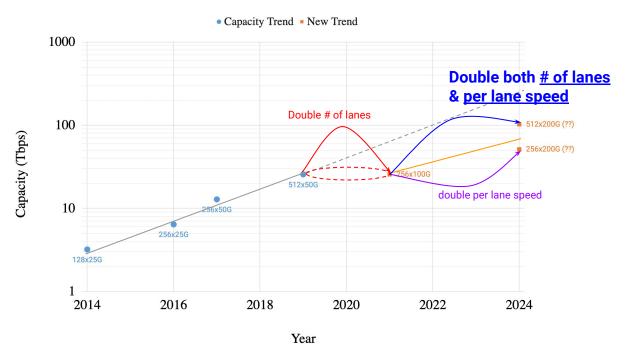

- Switch capacity growth slowed down due to limitation of power, SI and # of packaging pins

- 200Gbps/lane is critical to scale the switch bandwidth and efficiency of networking fabric.

## Pluggables for 200 Gbps per lane

#### Pluggable front panel ports provide:

- Evolutionary path for optics to 1.6Tbps/module (2x800G)

- Flexibility to optimize for various reaches: CR, SR, LR ...

#### Given front panel pluggable ports for optics:

=> next step is to explore feasibility copper cables in these ports

#### Channel Loss Budget: Key Components

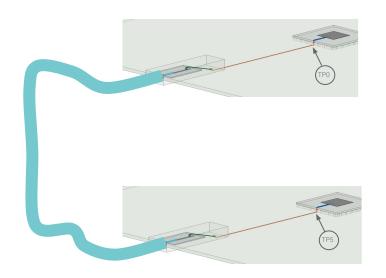

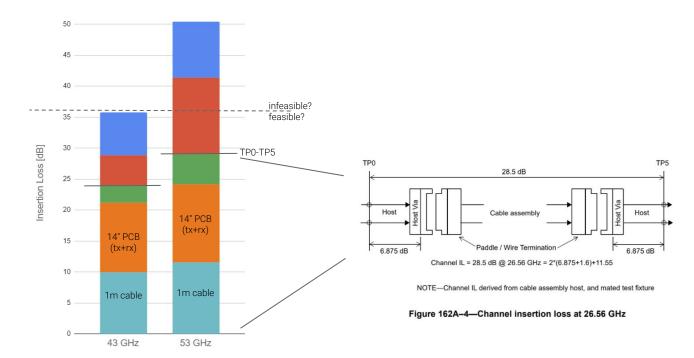

Channel is traditionally specified between TP0 and TP5 BGA/vias and packages are included in analysis

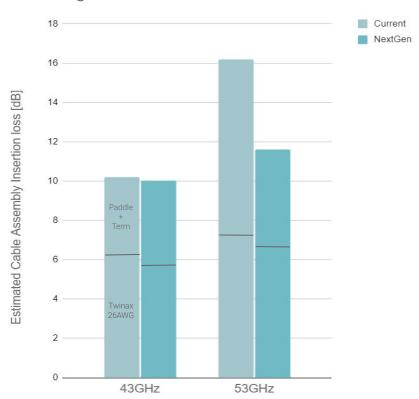

## Key Component: cable assembly\*

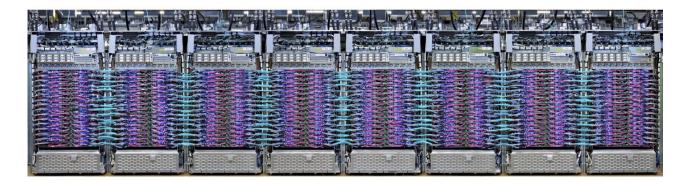

#### Engineered rackifications are key to managing cable lengths

- enforce long-to-short port combinations

- Key applications can be enabled by 1.0m cables

\*excluding connector

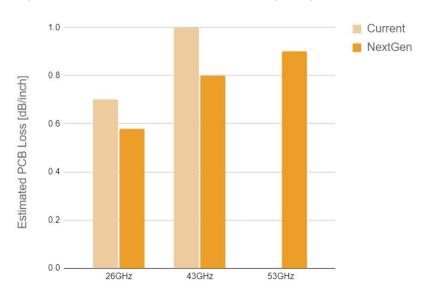

## Key Component: PCB trace loss

PCB differential pair loss improvements: evolutionary (no exotic materials)

- Wider trace with improved surface roughness

- Lower dielectric loss

Length reduction: port partitioning short/long

- Classic 32-port switch: ~9" long [1]; ~75% < 7"; ~60% < 5" (short) [2]

- Engineered rackifications: disallow long-long [3]

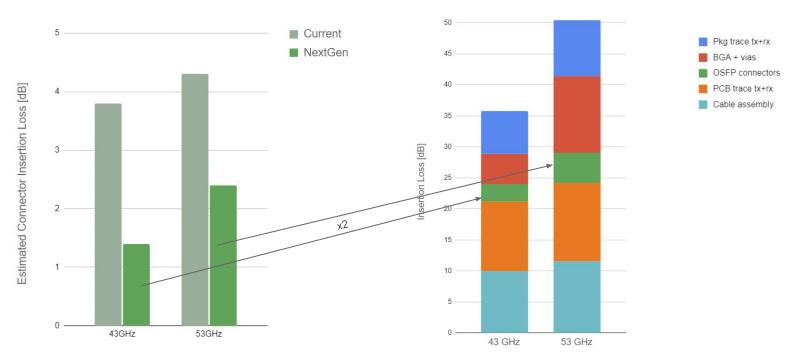

## Key Component: connector

OSFP200 MSA includes contributions on feasibility of connector Improvements focus on mating interface (stub, tolerance) as well as SMT interface

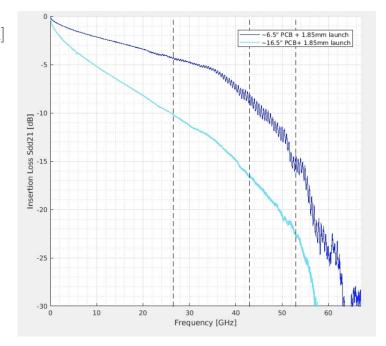

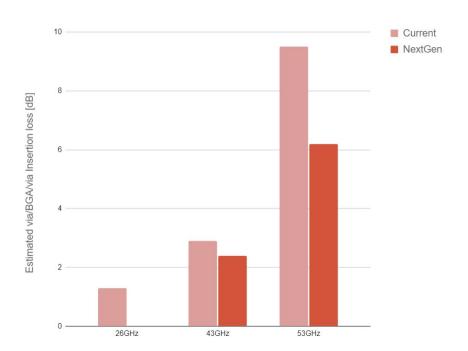

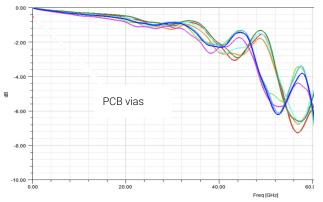

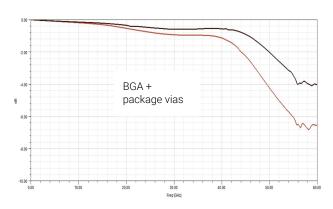

## Key Component: PCB vias, BGA, package vias

#### CALL TO ACTION: need cross-functional assessment

- Behavior strongly influenced by manufacturing capabilities

- Cross-sectional dimensions approach lambda/4 => over-moding

Simulations courtesy Leo Li, Google

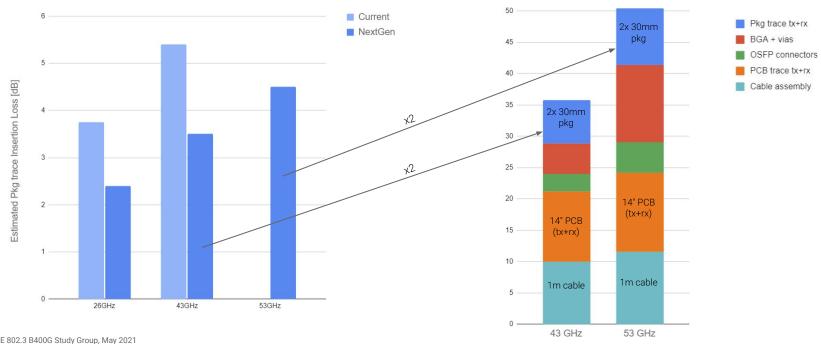

## Key Component: package differential pair

Package loss increasing disproportionately compared with prior generations

- based on large switch: 30mm package trace [4]

- asymmetric links (eg TOR-NIC) have shorter (eg 15mm) package trace

#### Link Budget

- <36dB bump2bump @ 43GHz: loss budget is promising

- >50dB @ 53GHz much more challenging; may be viable with serdes and BGA/via improvements

- Next steps: consider insertion loss deviation and crosstalk

- Passive copper cable at 200Gbps/lane seems feasible: ~36dB bump-to-bump for PAM6

- Need further technical analysis of channel, particularly for BGA/via impairments beyond 45GHz

- Serdes capabilities, FEC, and power efficiency not covered need full link analysis with channels informed by this feasibility study

Call for action: refine analysis of passive copper cable interface at 200Gbps/lane.

# THANK YOU!

#### References:

- [1] https://www.ieee802.org/3/100GEL/public/18\_03/stone\_100GEL\_01\_0318.pdf

- [2] https://ieee802.org/3/ck/public/18\_05/stone\_3ck\_01a\_0518.pdf

- [3] https://www.ieee802.org/3/ck/public/adhoc/apr28\_21/dawe\_3ck\_adhoc\_01\_042821.pdf

- [4] https://www.ieee802.org/3/100GEL/public/18\_03/lim\_100GEL\_01b\_0318.pdf

#### Contributors:

Kevin Zhang, Leo Li, Cedric Lam,