# IEEE 802.3af DTE Power via MDI Can Electronic Components Survive the High Voltages Associated with Safety and ESD Immunity Tests?

Proposal By PowerDsine: Avinoam Levy - avinoaml@powerdsineusa.com Rick Frosch - rickf@powerdsineusa.com

# **YES!!!**

# High Voltage Related Safety Standards Requirements EN60950, UL1950

- 3KVrms dielectric strength test, from AC input to RJ-45

- 500Vrms dielectric strength test, output to chassis

- Tests performed when unit is not operating

- These are standard requirements for off-line of the shelf power-supplies.

- Meeting these requirements will not impose real stress on the outputs of the PSE.

# High Voltage Related ESD Standard Requirements IEC-61000-4-2

- Up to 15KV charged on a human body simulated network - capacitor in series to resistor.

- The standard provides guidelines to select the appropriate class and hence the voltage level.

- Pass criteria defined by user, typically we design the equipment to survive with no performance degradation.

# Examples of Silicon Components Used in Similar Conditions and Applications

- SLIC Ic's (Subscriber Line Interface Card)

- Telephone Ring Generators

- Solid state relays used in telephony circuits

- Phone Ic's.

- Many more

#### **Protection Circuits**

Typically, components such as: Spark Gaps, Surge Arrestors, Transorbs and others are used in telephony circuits.

That will not be the case in our situation!

The Data Communication network is in much more benign conditions so the requirements are less severe.

### What are the Standard Requirements

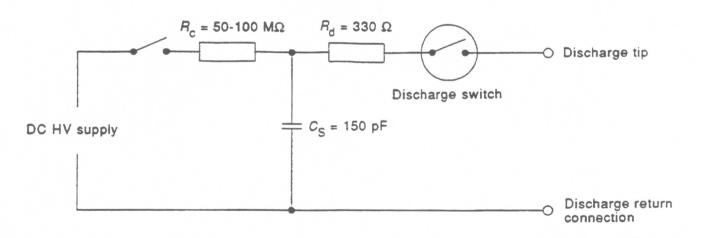

#### **ESD Generator**

61000-4-2 © IEC:1995+A1:1998

-35 -

IEC 001195

NOTE  $-C_0$ , omitted in the figure, is a distributed capacitance which exists between the generator and the EUT, GRP, and coupling planes. Because the capacitance is distributed over the whole of the generator, it is not possible to show this in the circuit.

Figure 1 - Simplified diagram of the ESD generator

# Voltage Levels

Table A.1 - Guideline for the selection of the test levels

| Class            | Relative humidity as low as | Antistatic<br>material | Synthetic<br>material | Maximum voltage   |

|------------------|-----------------------------|------------------------|-----------------------|-------------------|

| 1<br>2<br>3<br>4 | 35<br>10<br>50<br>10        | x<br>x                 | x<br>x                | 2<br>4<br>8<br>15 |

The installation and environmental classes recommended are related to the test levels outlined in clause 5 of this standard.

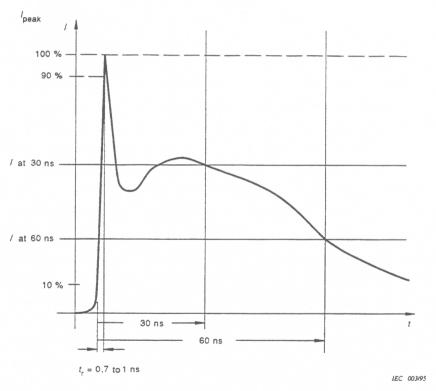

# Pulse Current Shape

Values are given in table 2.

Figure 3 - Typical waveform of the output current of the ESD generator

## **Application Method**

- Direct/Indirect discharge on accessible metal parts

- Indirect discharge on the accessible isolated parts

- Horizontal coupling plane

- Vertical coupling plane

In general, the direct discharge method is recommended, as it is more repetitive than air discharge.

## How do these Pulses Impact the Design?

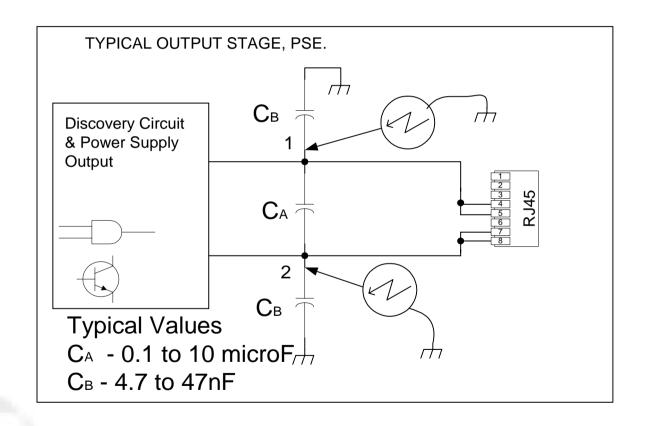

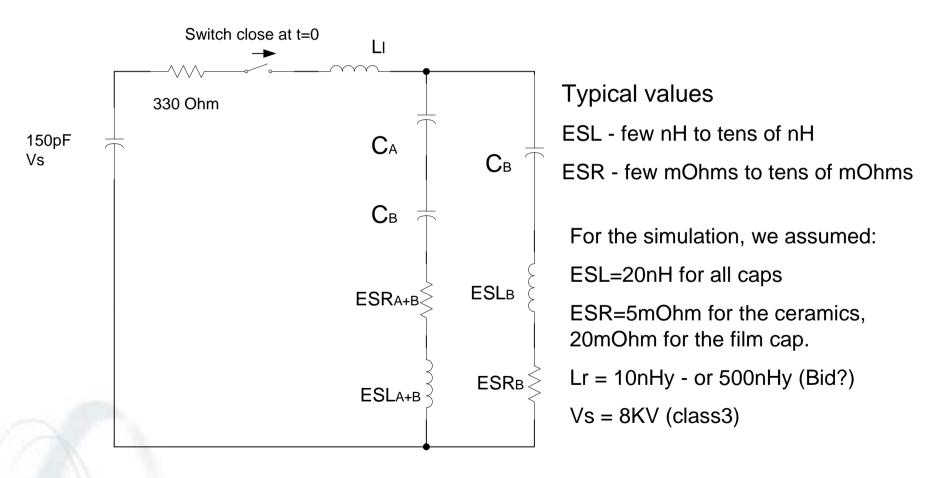

#### What do we have here?

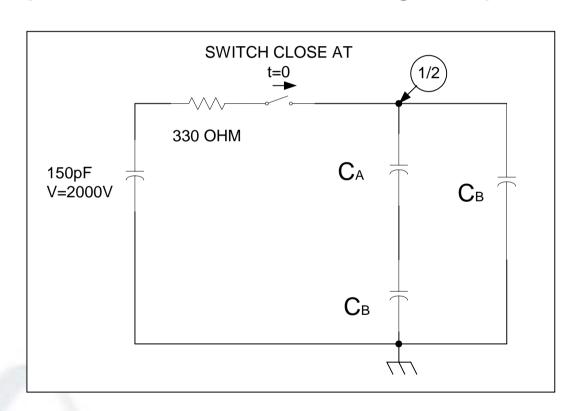

#### Equivalent circuit for discharge on point 1 or 2

#### Assuming:

$C_A$ = 0.47 $\mu$ F  $C_B$ = 0.0047 $\mu$ F As  $C_A$ >>  $C_B$   $C_A$ +  $C_B$  =  $C_B$ Total capacitance after switch close is  $\cong 2C_B$

#### Some calculations...

We know that:

$$Q @ t = 0^- = Q @ t = 0^+$$

$$Q = V * C \implies C1*V1 = C2*V2$$

TOTAL CHARGE IN THE SYSTEM BEFORE DISCHARGE EQUAL TO CHARGE AFTER DISCHARGE.

Where: C1=150pF, C2=2 $C_B$ , V1=V@t=0<sup>-</sup>=Vs=2KV and V2= $V_{1/2}$ @t=0<sup>+</sup>

$$\Rightarrow$$

V<sub>1/2</sub> @ t = 0<sup>+</sup> = 32V

$\Rightarrow$ V<sub>1/2</sub> is the voltage developed on the contact point (can be point 1 or 2 on the system schematics), referenced to the chassis.

For V @

$$t = 0^- = 8KV$$

,  $V_{1/2}$  @  $t = 0^+ = 127V$

#### Some more numbers...

Replacing CB to 10nF will reduce the developed voltage by 50%

As the charge is on the CB and CA branch is equal on both capacitors, the voltage across these two capacitors will be reveres proportional to its values. In our case, the voltage on CA - the cross output capacitor will be roughly 10% of the calculated voltage.

#### Let's add Real Life Conditions

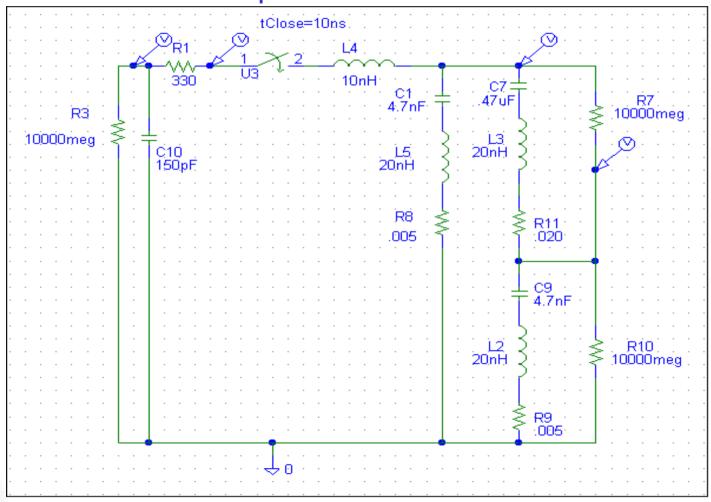

# Simulation Results - Spice Model

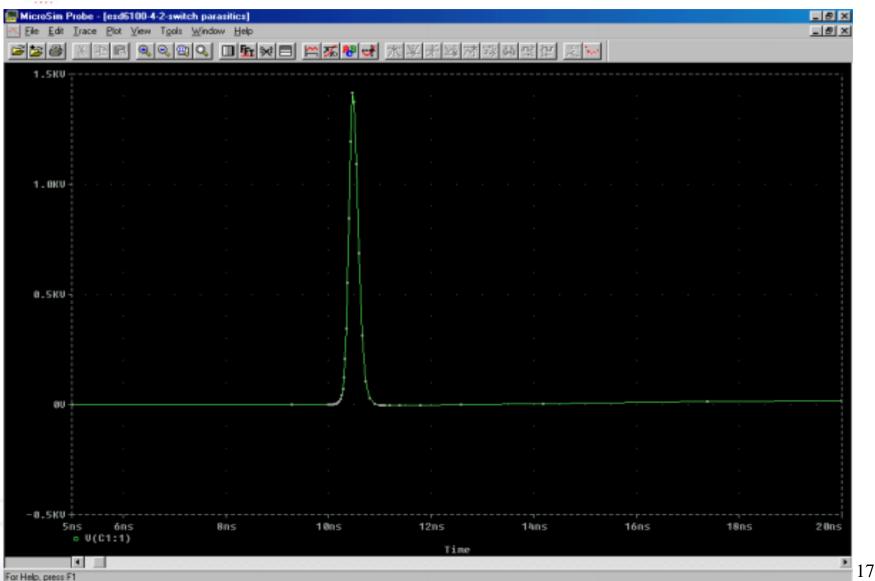

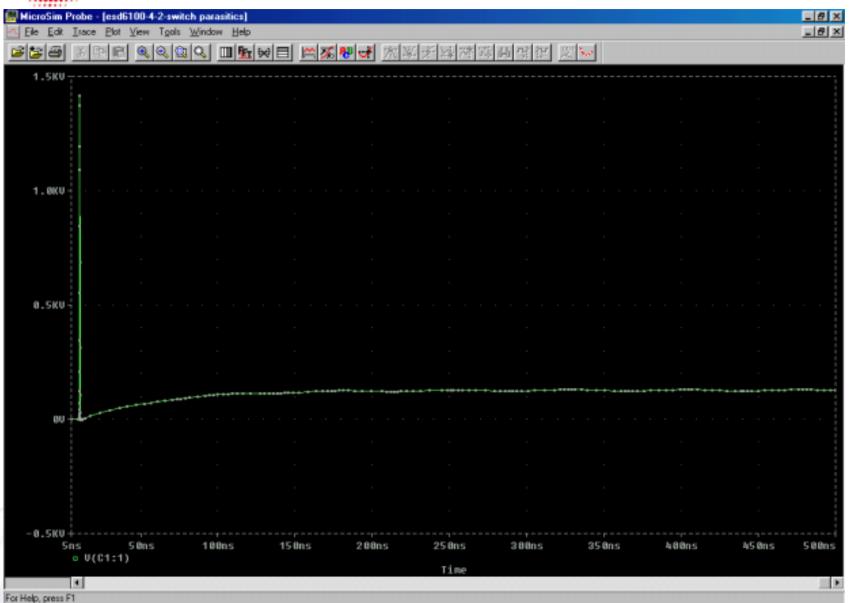

## Voltage Across Cap to Chassis (8kV Arc) Li= 10nH

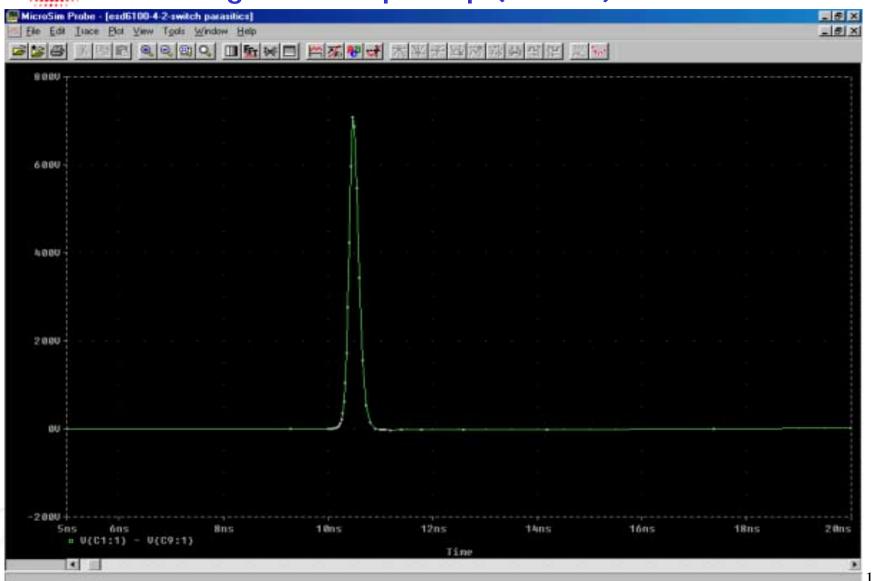

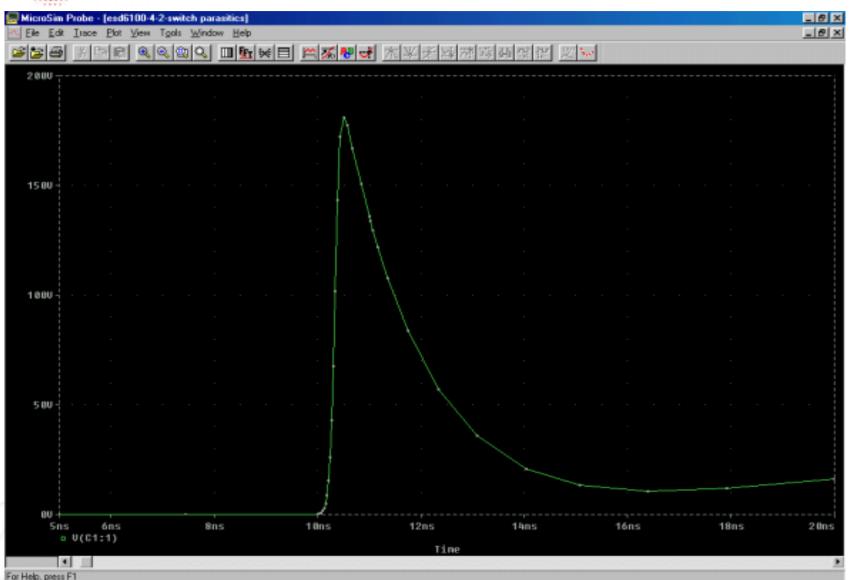

### Voltage Across Input Cap (8kV Arc) L<sub>I</sub> = 10nH

# oltage Across Cap to Chassis Steady State (8kV Arc), LI = 10nH

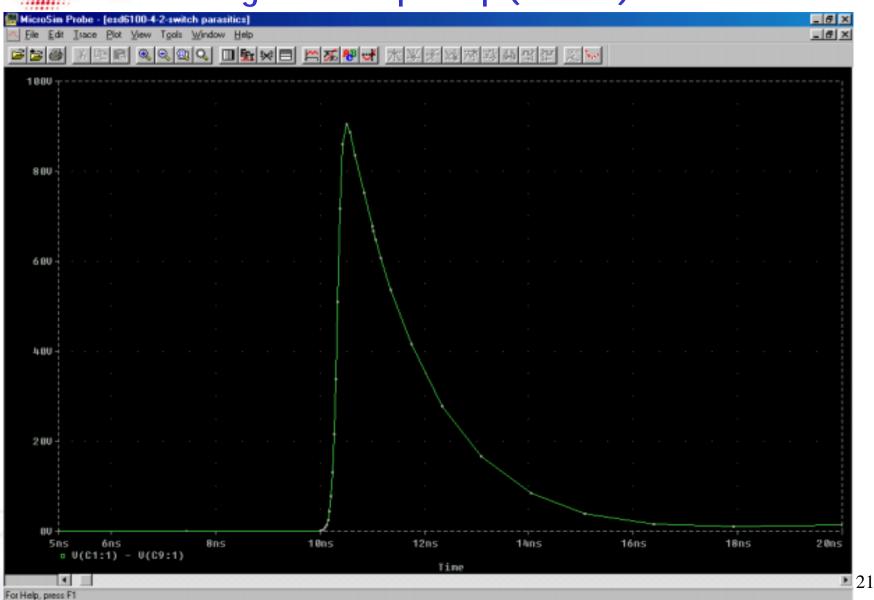

#### Voltage Across Cap to Chassis (8kV Arc) LI = 0.5uH

## Voltage Across Input Cap (8kV Arc) LI = 0.5uH

#### Conclusions

- The presentation showed that with typical power supply and typical feeding port elements the voltage stresses on the PSE components are within manageable limits.

- Some basic design guidelines where given to enable meeting Electro-Static-Discharge.

- Isolation transformer is not a must for a reliable PSE unit that will not degrade the ESD immunity of the network.

- A well protected and robust design is also economically feasible.