# Vport ad hoc discussion November 2006

# Fred Schindler Cisco Systems

Andrew Smith

Anoop Vetteth

Bill Delveaux

Brian Buckmeir

Chad Jones

Christain D. ?

Clay Stanford

Daniel Feldman

David Law

Derick Koonce

Frank Yung

Fred Schindler

Helen Kastner

Power Integration

Cisco Systems

Cisco Systems

Bel

Cisco Systems

ST Microelectronics

Linear Technology

PowerDsine

3COM

Independent

SystemX

Cisco Systems

Cisco Systems

Jean Picard

Keith Hopwood

Matthew Landry

Michael Altmann

Ramesh Sastry

Raul Lozano

Sajol Ghoshal

Taufique Ahmed

Thong Nguyen

Thuyen Dinh

Tim Parker

Wael Diab

Yair Darshan

Texas Instruments

Phihong

Silicon Labs

Akros Silicon

Cisco Systems

Pulse

Akros Silicon

Akros Silicon

Maxim

Pulse

Nortel Networks

Broadcom

PowerDsine

## **Agenda**

- di/dt

- Data collected.

- Current limits.

- An option for dealing with voltage transients.

- The need for new current limits and approach.

- Next step.

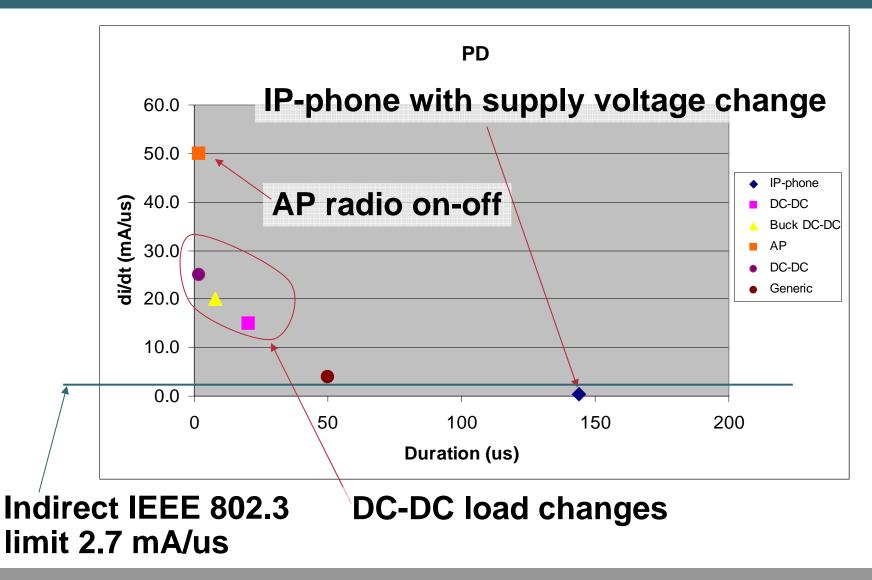

#### PD di/dt limits?

- 33.2.8.2 Load regulation

PSE dv/dt < 3.5 V/us @ di/dt = 35 mA/us</li>

- dv/dt = |Z| di/dt, |Z| = 100 ohms

- Table 33-5, item 3 and table 33-12 item 7.

< 1 MHz, Vpp < 0.1 Vpp</li>

dv/dt (max) = V<sub>p</sub>2πf = 0.3 V/uS

- PD di/dt limit. di/dt = dv/dt/R

di/dt = 0.3/(100 + 12.5) = 2.7 mA/us

- There are no PICS for PD di/dt limits.

## Sample PD di/dt values

## PD di/dt and PSE voltage droop

- Most sample PDs violate the indirectly calculated di/dt limit!

- Many PDs are UNH tested and pass.

- The di/dt threshold needs to be called out more directly.

- PD di/dt demands are supported by PD bulk capacitance or PSE output capabilities.

- The PSE voltage droop permissible and the maximum cable current help determine whether the PD bulk capacitance or the PSE output provide the current demanded.

$V_{PD}$

To DC-DC

PD IC

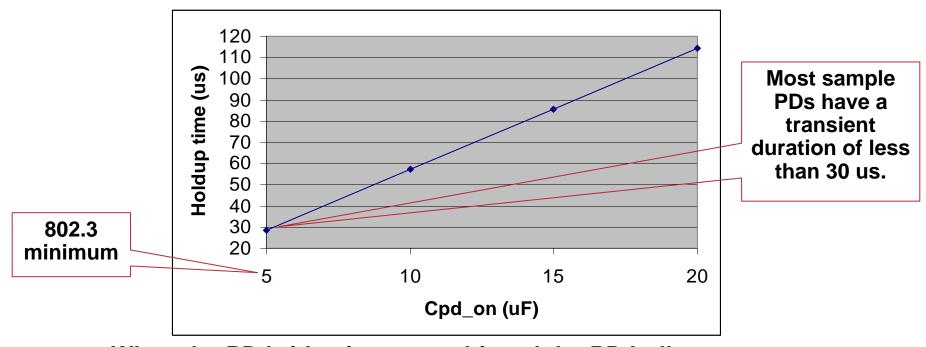

#### **Fast transients**

When the PD bridge is reverse biased the PD bulk capacitance provides the PD power.

Sample PDs with durations 50 uS or longer have a di/dt of less than 5 mA/us and result in less than a 5%  $V_{\rm PSE}$  change for PSEs in the sample set.

dt = CdV/I, I =  $I_{LIM\ MIN}$  = 840 mA, at this current a 30 W PD has at least 36 V at its input.

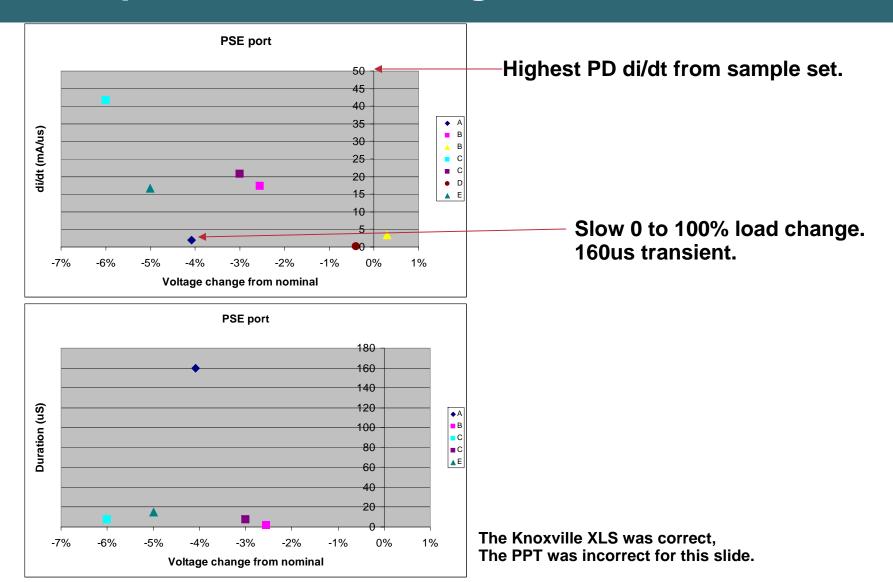

## Sample PSE load change effects

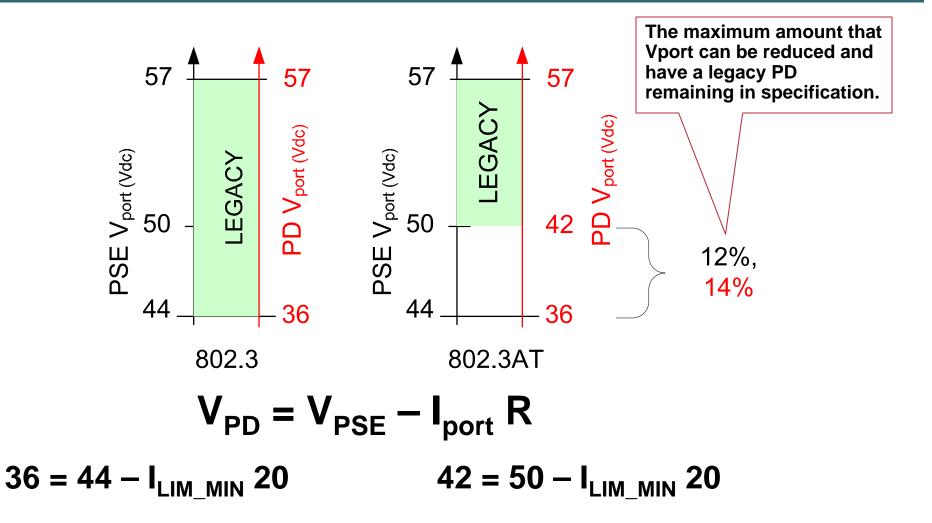

## **Legacy PD**

$I_{LIM\_MIN} = 400 \text{ mA}$

#### **30W PD**

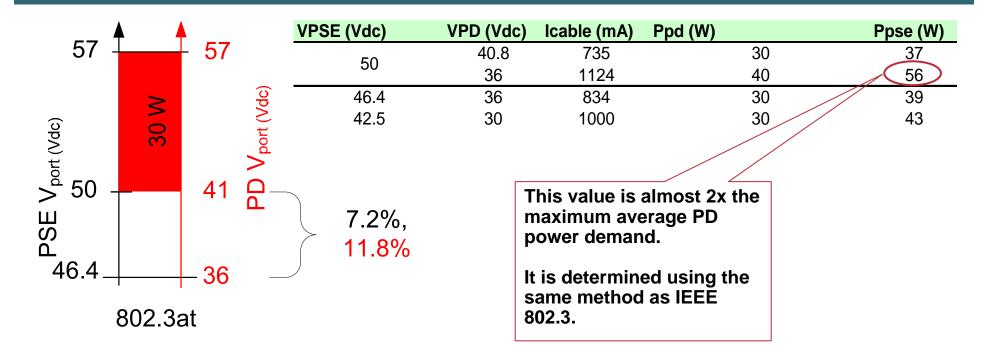

Do we want new PDs to operate at a lower port voltage than legacy devices?

The largest droop for the sample PSEs is 6%.

## I<sub>CUT</sub> and I<sub>LIM</sub> thresholds

- None of the sample PDs cross the I<sub>cut</sub> threshold.

- I<sub>CUT</sub> = P<sub>PSE\_MIN</sub>/V<sub>port</sub> ,(<5% duty cycle at the PD)</li>

- I<sub>LIM</sub> is a fix value not related to V<sub>port</sub>.

- These current thresholds exist to permit the PD to draw more power than their reported average power.

- All sample PD current transients are less than

150 uS, while PSE voltage transients are less than 200 uS.

- TLIM and Tovld are approximately 250x larger than the largest transient.

- The current thresholds and the purpose of these currents need to be evaluated for this extension to PoE.

### **Next Step**

- Determine how to better convey PD di/dt rate limits.

- Determine what the PD di/dt limits should be.

- Collect more PD and PSE system input.

- Review current thresholds and their purpose.

- Adjust recommendations based on cable limit data.

- Determine what channel model the AF specification should use.

**Based on V11 Spreadsheet.**