# Physical Aspects of Packages for 100GEL & PKG ad-hoc Physical Aspects Summary

Liav Ben Artsi, Marvell Israel Ltd. September 2018

## Suggested PKG Model Cases

|                                            | Length | Ball Side<br>Discontinuity | Xtalk (Suggest using random noise) | Suggested Decision & (Priority)                                                             |

|--------------------------------------------|--------|----------------------------|------------------------------------|---------------------------------------------------------------------------------------------|

| PHY (WIP)                                  | 8-12mm | Low Pitch BGA              | High                               | A Must have for high reflections & Xtalk (1)                                                |

| Typ Switch                                 | 20mm   | 1mm pitch BGA              | Medium                             | Check if covered by any of the 30mm (2)                                                     |

| High Lane Count<br>Switch up to<br>70x70mm | 30mm   | 1mm pitch BGA              | Low                                | Provide an initial model to check for impact (1)                                            |

| High Lane Count<br>Switch > 70x70          | 30mm   | LGA                        | Low                                | Discuss whether should<br>be covered. if yes<br>How?<br>If not how to manage<br>the impact? |

Models supplied for Case 1 & 3 and dealt with until now

## PKG Trace & Design Characteristics

29 micron width for low loss Dielectric loss coefficient = 0.004 Roughness processing causes R=0.1µ on the treated surface 90ohm nominal targeted PKG impedance a long PKG traces it was assumed that dominant Xtalk can be avoided due to big package size in this case (though in some situations that may not be the case) Xtalk (Fext only) will be taken only in the short PKG trace IEEE P802.3ck 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

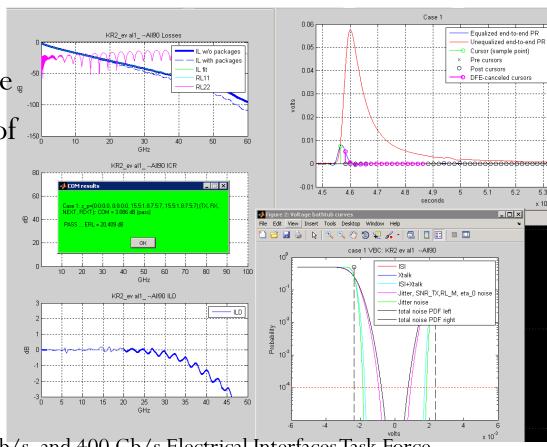

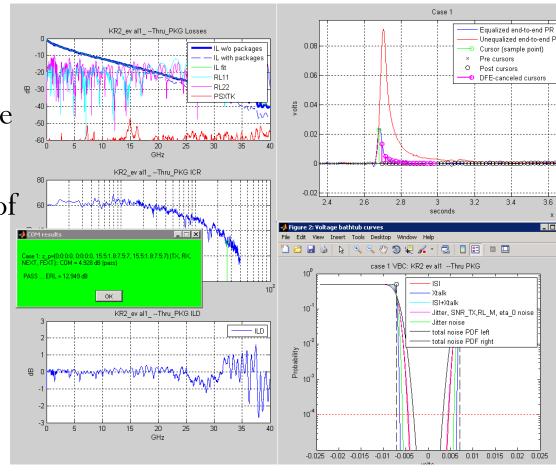

#### COM Runs on Concatenated Interconnect + PKGs

- Nb=16

- Cd = 130fF / 110fF (10fF included in PKG extracted model)

- Ran with 30mm HFSS extracted PKGs on both ends

- Ball + PTH discontinuity integrated into the extracted model

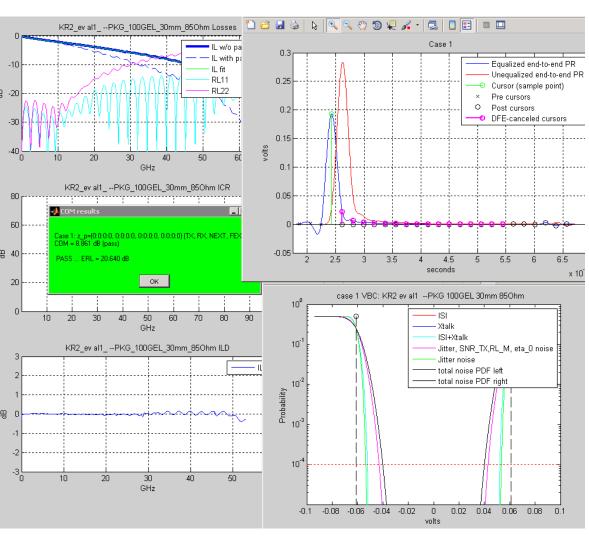

#### Ideal 30mm PKG

Concatenated to 30mm packages on both sides

•  $\sim$  90 $\Omega$  trace

• 130fF total die capacitance

Ball capacitance is a part of The Extracted Model

• 3.1dB COM

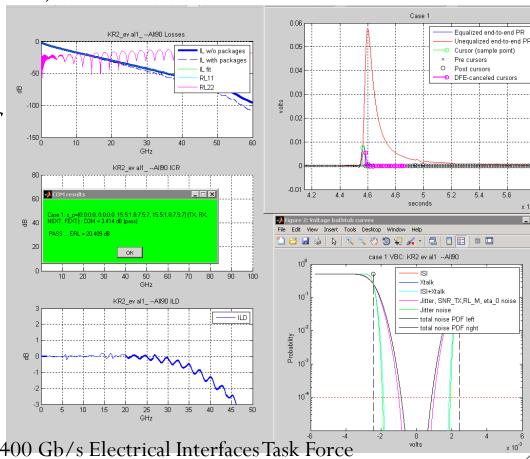

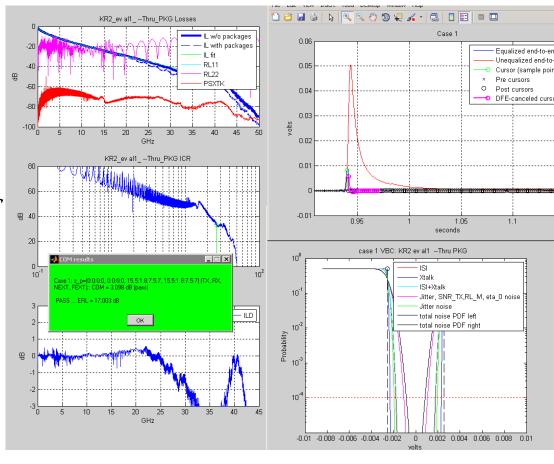

## Best Design 30mm PKG

- Concatenated to 30mm packages on both sides

- $\sim$ 90 $\Omega$  trace (28dB@26.6GHz)

- 110fF total die capacitance (100fF-Die + 10fF-PKG)

- Ball capacitance is a part of The Extracted Model

- ~3.4dB COM

## ~90Ω PKG Results (Stand Alone)

Die Side totalcapacitance = 110fF

No BRD attached

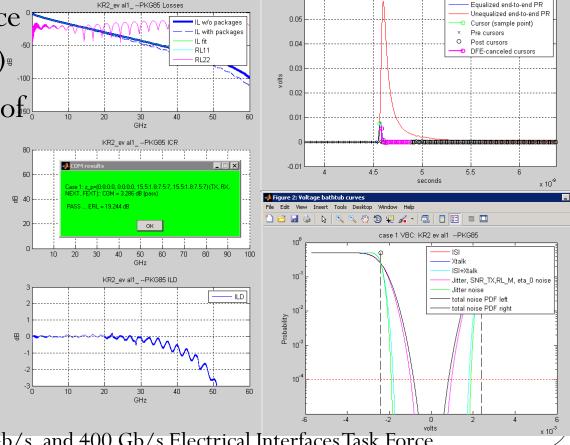

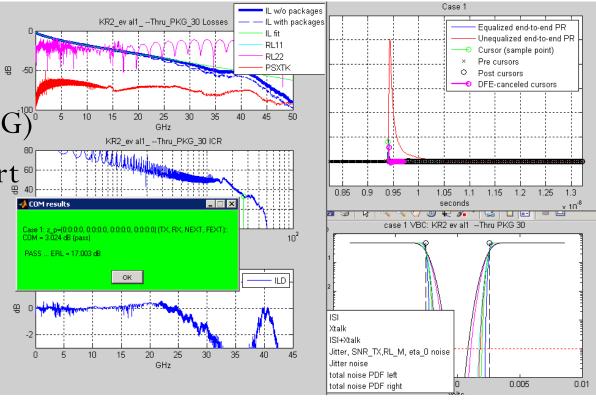

## ~85Ω PKG 30mm length

Die Side total capacitance = 110fF

No BRD Attached

IEEE P802.3ck 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

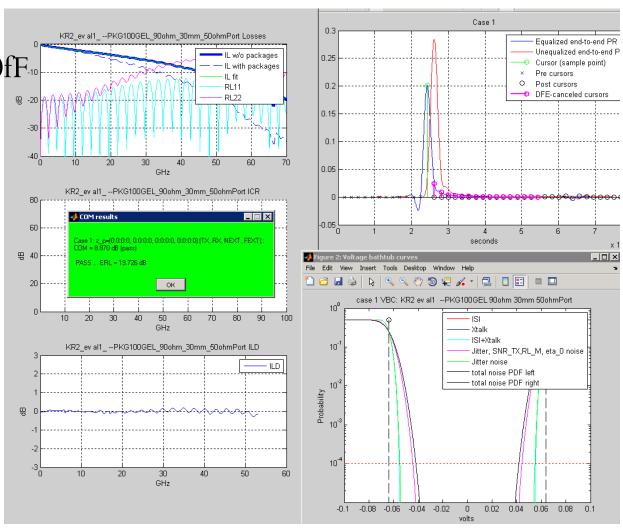

#### PKG85

• Concatenated to 30mm  $85\Omega$  packages on both sides

•  $\sim$ 90 $\Omega$  trace (28dB@26.6GHz)

• 110fF total die capacitance (100fF-Die + 10fF-PKG)

• Ball capacitance is a part of The Extracted Model

• ~3.4dB COM

0.06

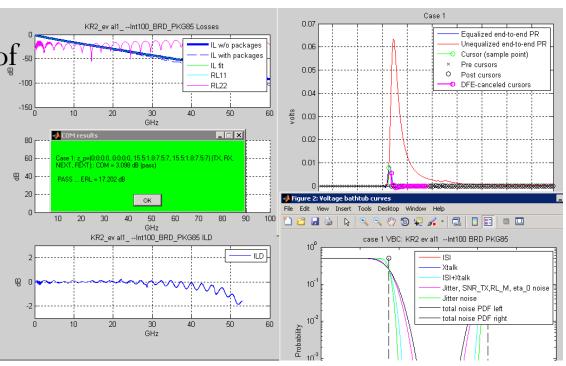

#### PKG85 + 100ohm MEG6 BRD

- Concatenated to 30mm  $85\Omega$  packages on both sides

- $100\Omega$  max loss trace (MEG6 28dB@26.6GHz)

- 110fF total die capacitance (100fF-Die + 10fF-PKG)

- Ball capacitance is a part of The Extracted Model

- ~3.1dB COM

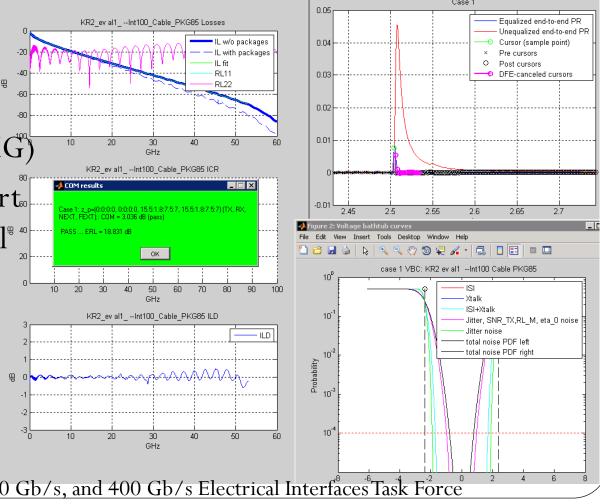

#### PKG85 + 100ohm Twinax Cable

• Concatenated to 30mm  $85\Omega$  packages on both sides

$100\Omega$  max-loss cable

• 110fF total die capacitance (100fF-Die + 10fF-PKG)

Ball capacitance is a part of the Extracted Model®

• ~3.1dB COM

## PKG85 + Lim\_16dB

• Concatenated to  $30 \text{mm } 85\Omega$  packages on both sides

- 16dB loss C2M channel

- 110fF total die capacitance (100fF-Die + 10fF-PKG)

- Ball capacitance is a part of The Extracted Model

- ~4.9dB COM

(can therefore run with lower silicon capabilities)

#### PKG85 + CaBP\_BGAVia\_Opt2\_28dB

- Concatenated to  $30 \text{mm } 85\Omega$  packages on both sides

- $100\Omega$  max loss trace

- 110fF total die capacitance (100fF-Die + 10fF-PKG)

- Ball capacitance is a part of the extracted model

- ~3.1dB COM

### PKG85 + CaBP\_BGAVia\_Opt2\_28dB+ XTalk

• Concatenated to 30mm  $85\Omega$  packages on both sides

Concatenated to CaBP\_BGA\_Opt2\_28dB which includes

BGA break-out via

• 110fF total die capacitance (100fF-Die + 10fF-PKG)

• Ball capacitance is a part of the extracted model

~3dB COM including

5Fext + 3Next

#### PKG85 + CaBP\_BGAVia\_Opt2\_32dB

ullet Concatenated to 30mm 85 $\Omega$ 0.045 packages on both sides Equalized end-to-end PR IL w/o package: Unequalized end-to-end PR Cursor (sample point) Pre cursors •  $100\Omega$  max loss trace RL22 DFE-canceled cursors • 110fF total die capacitance (100fF-Die + 10fF-PKG) Ball capacitance is a part of 📣 Figure 2: Voltage bathtub curves The Extracted Model 20 🚵 | 🔈 🔍 🤏 🖑 🐌 🖳 🗗 🔲 💷 💷 case 1 VBC: KR2 ev al1 -- Thru PKG • ~1.3dB COM 10 - Xtalk Jitter, SNR TX,RL M, eta 0 noise total noise PDF left IEEE P802.3ck 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Task Force

#### Nominal or WorstCase?

- None... Not nominal and not worst case, rather a good design and "a bit of" manufacturing tolerance. (Can we allow a bit more tolerance? The model places us in a sweet spot... should we ask for more tolerance? Should we include Xtalk in the long PKG as well?)

- 8mm/12mm PKG model should follow the same concept as the 30mm but integrate Xtalk into both Rx and Tx sides (FEXT alone) to account for the small PKG footprint/size

- $\bullet$  Crosstalk per PKG case suggested to be implemented as random noise with the applicable  $\sigma$

## Future Large 100G/lane Devices

- Not Covered by the model, but the model does not seem to have that margin @ this point

- Big packages will be one possible target implementation for 100Gbps/lane

- Need to consider the implications of a decision not to model future LGAs

- <a href="https://www.ectc.net/files/68/ECTC">https://www.ectc.net/files/68/ECTC</a> 2018 Luncheon Keynote BCOoi Broadcom.pdf

| IC Package Need   | 2018                | 2022                             | Challenges                                                                                                              |

|-------------------|---------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Data Rate         | 56 Gbps             | 112 Gbps                         | Channel Insertion Loss & Return Loss Crosstalk Power Integrity                                                          |

| Body Size         | 67.5mm x<br>67.5 mm | > 90mm x<br>90mm                 | <ul> <li>Package Warpage</li> <li>Board Level Reliability</li> <li>Socket Cost &amp; Performance<br/>Penalty</li> </ul> |

| 2.5D Integration  | Up to 5 dies        | More/Larger dies (incl. Optical) | Interposer Reticle Size     Assembly challenges     More Memory BW                                                      |

| Micro-bump Pitch  | 40um                | <=30um                           | <ul><li>Assembly challenges</li><li>Routing challenges</li></ul>                                                        |

| Power Dissipation | 300 W               | > 500 W                          | Thermal Interface Material     Heatsink Solutions                                                                       |

## Summary

• It was shown that a well designed 30mm  $85\Omega$  (90 $\Omega$  with "some" manufacturing tolerance) PKG can pass the target interconnect with 3dB COM