## In support of comments #8, 9, 10, 11 against D1.2

David Lewis, Lumentum

Nov 15<sup>th</sup>, 2021

IEEE P802.3cw 400 Gb/s over DWDM systems Task Force

# Comment #8: Need detailed functions and state machines at 155.4

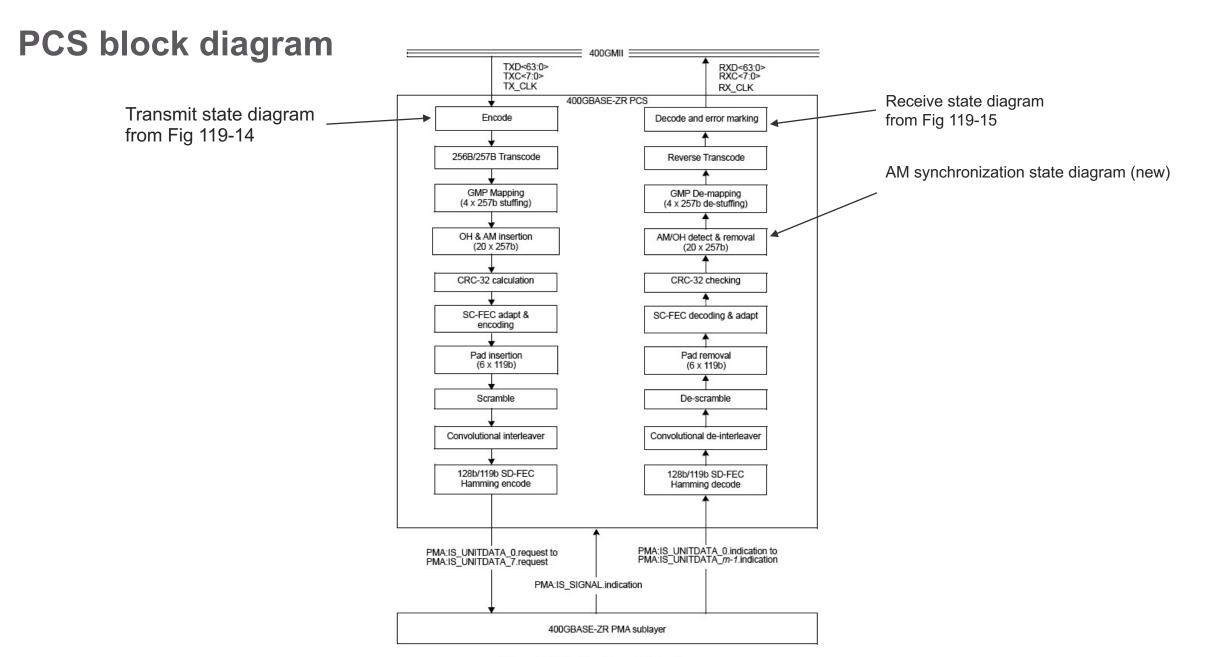

Figure 155-2-Functional block diagram

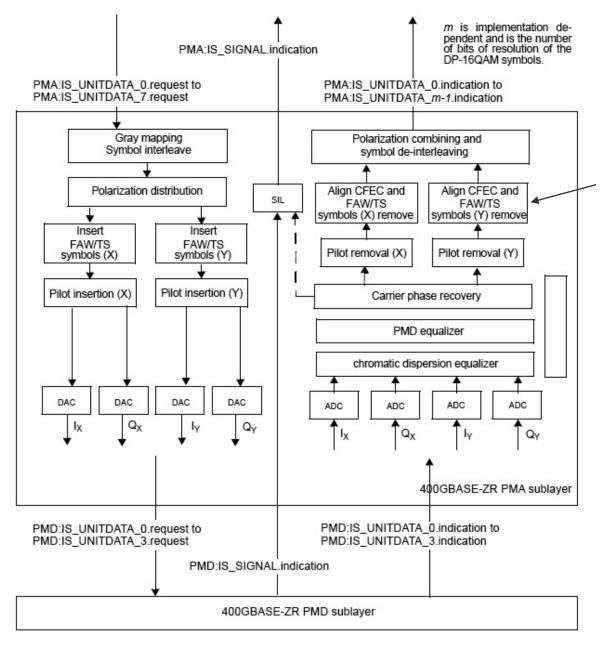

### **PMA** block diagram

DSP FAW synchronization state diagram and PMA deskew state diagram (new)

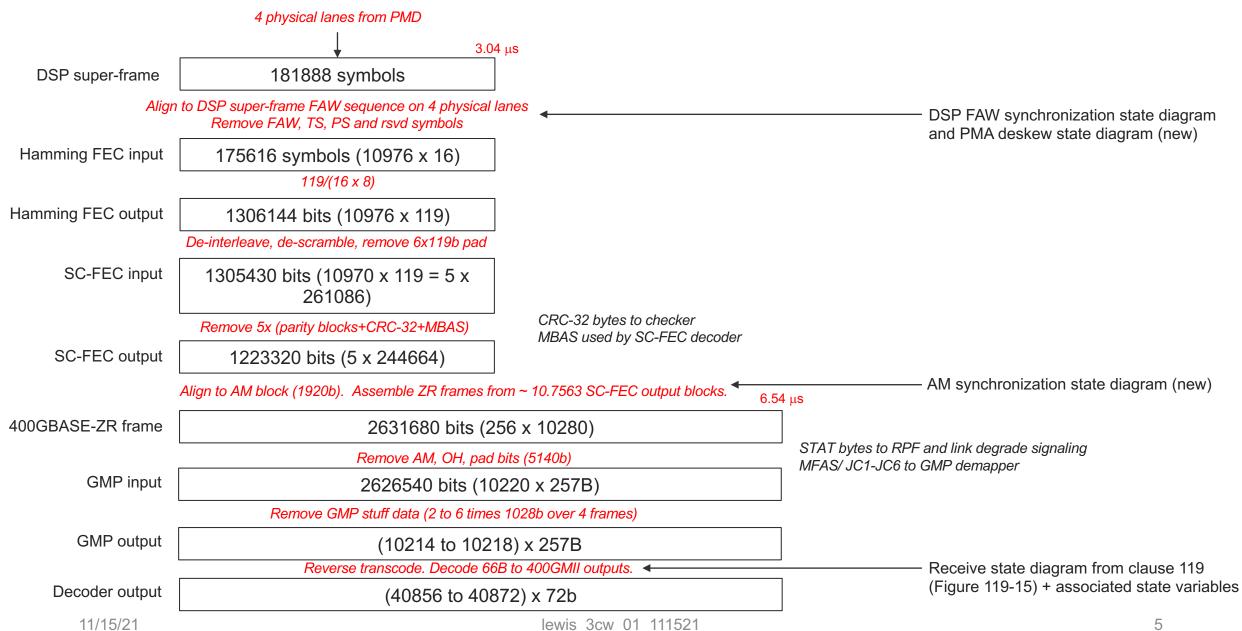

## Where are new state diagrams needed? PCS receive direction

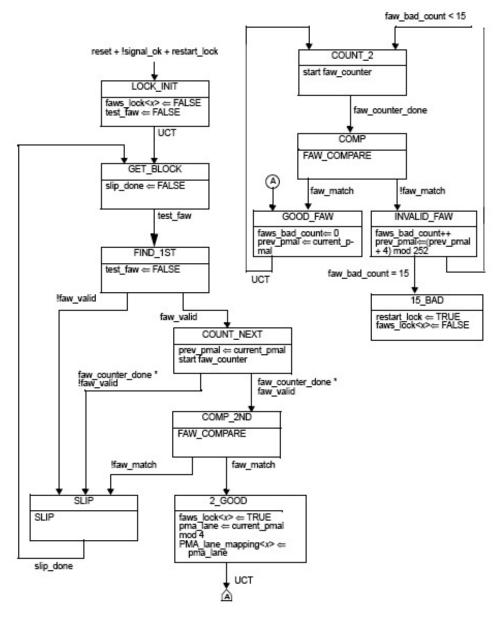

## **DSP FAW lock state diagram**

- Based on 802.3ct Figure 153-7 with fas replaced by faw, and fecl replaced by pmal

- 4 lanes instead of 20

Figure 155-13-DSP FAW synchronization state diagram

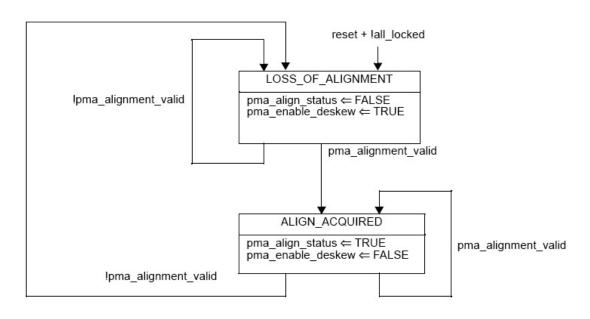

### PMA deskew state diagram

Based on 802.3ct Figure 153-8 with fec\_align replaced by pma\_align

Figure 155-14—PMA deskew state diagram

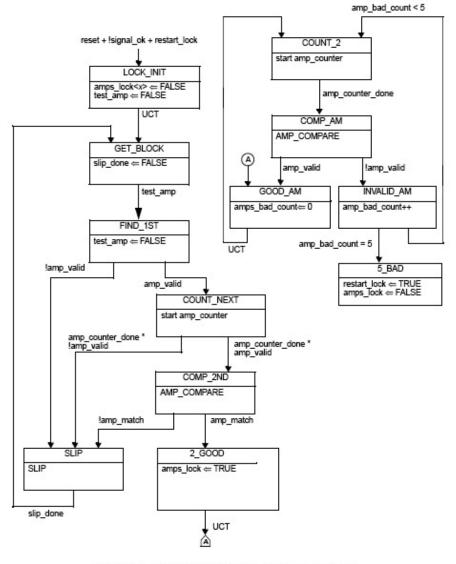

## Alignment marker lock state diagram

- Based on Figure 119-12 (400GBASE-R PCS) but for a single lane

- No need for lane mapping

- Look for all 1920 bits (16x120) instead of just a single 120-bit sequence?

Figure 155-15-Alignment marker lock state diagram

### **Accompanying proposed text:**

### 155.4 400GBASE-ZR PCS and PMA detailed functions and state diagrams

Editor's Note (to be removed prior to publication): Task force has not yet considered a baseline for detailed functions and state diagrams.

The body of this subclause includes state diagrams, including the associated definitions of variables, functions, and counters. Should there be a discrepancy between a state diagram and descriptive text, the state diagram prevails.

The notation used in the state diagrams follows the conventions of 21.5. The notation ++ after a counter or integer variable indicates that its value is to be incremented.

### 155.4.1 State variables

### 155.4.1.1 Variables

align status amp counter done amp match amp valid amps\_lock cw bad hi ser PCS status rx local degraded rx rm degraded

### all locked

A Boolean variable that is set to TRUE when faws lock x> is TRUE for all x and is set to FALSE when faws lock < x> is FALSE for any x.

A variable that holds the PMA lane identification octet corresponding to the current FAW that is recognized on a given lane of the PMA service interface. The value of this variable modulo 4 represents the PMA lane number. It is compared to the expected value based on the variable prev pmal to confirm that the location of the FAW has been detected. This value is interpreted with the most significant bit transmitted first

### faws counter done

Boolean variable that indicates that faws counter has reached its terminal count.

### faw match

Boolean variable that holds the output of the function FAW COMPARE.

Boolean variable that is set to TRUE if the received 22-symbol sequence is a valid FAW. The FAW consists of one of the sequences listed in Table 155-3. The sequence is considered to be valid if at least TBD symbols match the known bits of the pattern described in 155.3.3.3.1.

Boolean variable that is set to TRUE when the receiver has detected the location of the FAW for a given lane on the PMA service interface, where x = 0.3.

A Boolean variable set by the PMA alignment process to reflect the status of PMA lane-to-lane alignment. Set to TRUE when all lanes are synchronized and aligned and set to FALSE when the deskew process is not complete.

### pma alignment valid

Boolean variable that is set to TRUE if all PMA lanes are aligned. PMA lanes are considered to be aligned when faws lock <x> is TRUE for all x, each PMA lane has a unique lane number, and the PMA lanes are deskewed. Otherwise, this variable is set to FALSE.

A Boolean variable that indicates the enabling and disabling of the deskew process. Data may be discarded whenever deskew is enabled. TRUE when deskew is enabled. FALSE when deskew is

### pma lane

A variable that holds the PMA lane number (0 to 3) received on lane x of the PMA service interface when faws lock<x> = TRUE. The PMA lane number is determined by matching the received 22symbol sequence to the values in one of the columns of Table 155-3, interpreted with the most significant bit transmitted first, modulo 4. It is set to current pmal modulo 4 when the expected FAW is found in the expected location in a second consecutive DSP super-frame.

### PMA lane mapping < x>

This variable indicates which PMA lane is received on lane x of the PMA service interface when faws lock< x > = TRUE where x = 0.3

A variable that holds the value of the lane identification octet (or the expected value of the lane identification octet) from the previous DSP super-frame. The value is interpreted with the most significant bit transmitted first. The lane represented is this value modulo 4. It is used to calculate the expected value of the lane identification octet in the next DSP super-frame period that is tested.

Boolean variable that controls the resetting of the PMA sublayer. It is TRUE whenever a reset is necessary including when reset is initiated from the MDIO and during power on.

### restart lock

Boolean variable that is set by the PMA alignment process to reset the synchronization process on all PMA lanes. It is set to TRUE when 15 FAWs in a row fail to match (15 BAD state).

Boolean variable that is set by the receive signal processing function (see 155.3.3.6).

### signal ok

Boolean variable that is set based on the most recently received value of PMA:IS SIGNAL indication (SIGNAL OK). It is TRUE if the value was OK and FALSE if the value was FAIL.

### slip done

Boolean variable that is set to TRUE when the SLIP requested by the DSP FAW synchronization state diagram has been completed indicating that the next candidate FAW position can be tested.

Boolean variable that is set to TRUE when a candidate FAW position is available for testing and FALSE when the FIND 1ST state is entered.

### 155.4.1.2 Functions

### AMP COMPARE FAW COMPARE

This function compares the FAW with its expected value to determine if a valid frame alignment word sequence has been detected and returns the result of the comparison using the variable faws match. FAW COMPARE is TRUE if faw valid is TRUE, and current pmal (interpreted with the most significant bit transmitted first) is equal to the prev pmal plus 4 modulo 252. Otherwise, faws match is FALSE.

### SLIP

Causes the next candidate FAW position to be tested. The precise method for determining the next candidate FAW position is not specified and is implementation dependent. However, an implementation shall ensure that all possible frame alignment word positions are evaluated.

### 155.4.1.3 Counters

Counts the number of consecutive AM blocks that don't match the expected value.

Counts the interval of 10 240 257B blocks containing normal AM sequences.

Counts the number of uncorrected SC-FEC codewords. This counter is set to zero when an SC-FEC codeword is received and cw bad is false.

Counts the number of consecutive FAWs that don't match the expected value for a given PMA

### faw counter

Counts the 181 888 symbols between the starting position of one FAW and the expected starting position of the next FAW on a PMA lane. This counter starts with a value of zero when start faw counter is asserted (at the position of the first symbol of a matched FAW pattern on a PMA lane), is incremented for each symbol on that PMAlane, and reaches a terminal value of 181 888 at the expected position of the next FAW pattern on that PMA lane.

### 155.4.1.4 State diagrams

The PMA shall implement 4 DSP FAW synchronization processes as shown in Figure 155-13 to identify the boundaries of DSP super-frames by observing the stream of symbols on four physical lanes. The synchronization process operates independently on each lane. The synchronization state diagram determines when the PMA has detected the location of the frame alignment word sequence in the received symbol stream for a given lane of the PMA service interface.

The PMA shall also implement the deskew process as shown in Figure 155-14.

The PCS shall implement the alignment marker lock process as shown in Figure 155-15 to identify the AM sequence at the start of each 400GBASE-ZR frame by observing data from the SC-FEC decoder output.

## Comment #9: Need management information at 155.5.

Defer to next meeting, pending decision on state machines (comment #8)

## Comment #10: Need loopback information at 155.6.

Defer to next meeting, pending decision on state machines (comment #8)

## Comment #11: Need PICs tables at 155.8.

Defer to next meeting, pending decision on state machines (comment #8)