# 53 Gbaud VCSEL MMF System Measurements on Impact of Rx C2M Channel Loss in a Linear Interface

Ariel Nachum, Jennifer Wu, and Ilya Lyubomirsky, Inphi Corp. IEEE P802.3db 100 Gb/s, 200 Gb/s, and 400 Gb/s Short Reach Fiber Task Force Interim Teleconference, Oct. 29, 2020

## Introduction

- A linear interface has been proposed in latchman\_3db\_adhoc\_01\_100120 and latchman\_3db\_adhoc\_01\_101520. However, there is lack of 53 Gbaud PAM4 endto-end experimental data to demonstrate technical feasibility

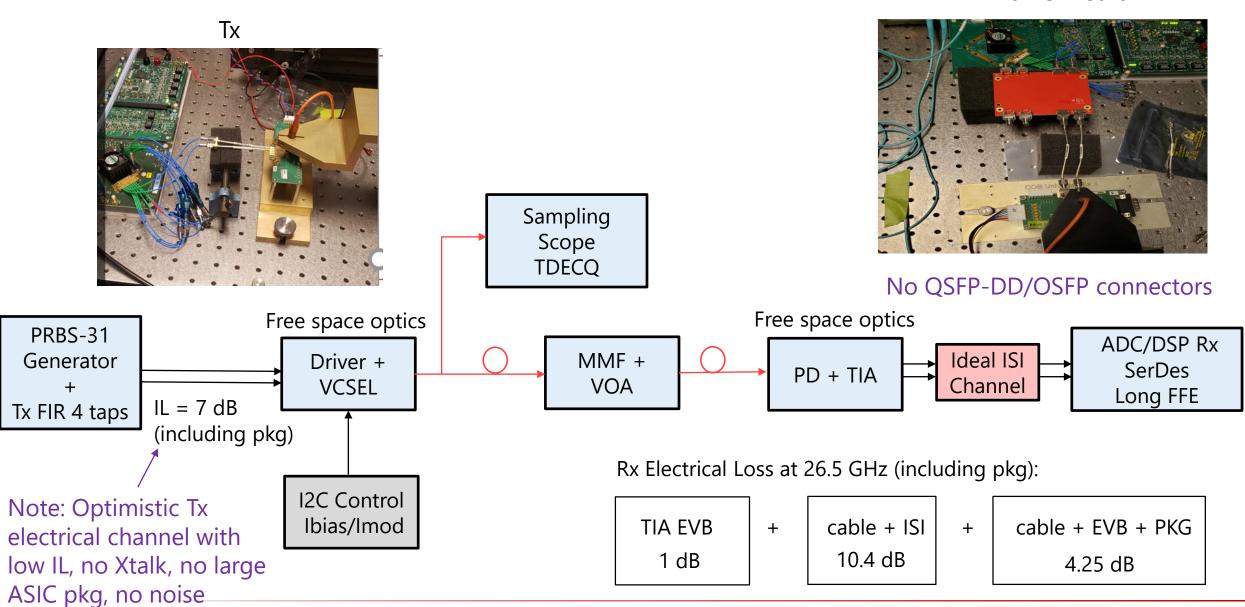

- In this work, we present 53 Gbaud PAM4 end-to-end system measurements including both optical VCSEL/MMF channel, as well as electrical ISI channel to emulate the C2M loss at Rx

- Due to lack of availability of QSFP-DD/OSFP mated board, the measured Rx C2M channel is an ideal ISI channel

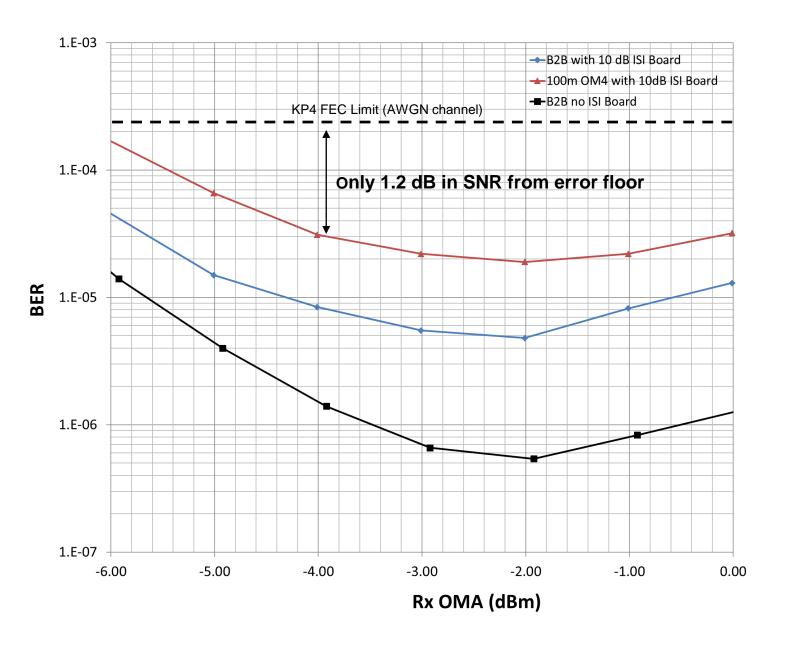

- The measurement results show even with an ideal Rx C2M channel, the system is not realizable due to severe error floor

## 53Gbaud VCSEL Experimental Setup

penalty from a CTLE

#### Rx with ISI Board

## Tx TDECQ Measurement (5-tap FFE)

### Measurement Results

#### Impairments <u>not</u> included in experiment:

- Realistic Tx C2M channel loss

- QSFP-DD/OSFP connector at Tx/Rx

- Electrical Xtalk

- PVT penalties (e.g. VCSEL measured at room temp.)

- Component aging

## **Conclusions**

- 53 Gbaud PAM4 end-to-end system BER measurements show significant penalty for Rx electrical loss in a linear interface

- The data shows an error floor at BER = 3.e-5, with very little margin for expected additional system penalties due to Tx C2M channel, electrical Xtalk, electrical reflections, PVT corners, and device aging

- Future experiments will include a mated QSFP-DD/OSFP test board for more realistic C2M channel at both Tx and Rx