# Framing for Asymmetric Ethernet links

Elvio Serrano, Alireza Razavi, Ragnar Jonsson

10/10.2024

### Contributors

- Paul Fuller (Marvell)

- Peter van Dyck (Marvell)

- Bizhan Abedinzadeh (Marvell)

- Alejandro Castrillon (Marvell)

### Introduction

- ACT design has already shared in the last standard meeting

- High data rate (HDR) path framing matches the 802.3ch specification

- In this presentation, we go over the framing for both data mode and training in low data rate (LDR) path

- https://www.ieee802.org/3/dm/public/0924/jonsson 3dm 01 09 15 24.pdf

## Framing objectives and assumption

- The framing that supports

- FEC latency < 2us</p>

- Burst error correction > 50ns

- No OAM is needed for side channel (from switch to camera)

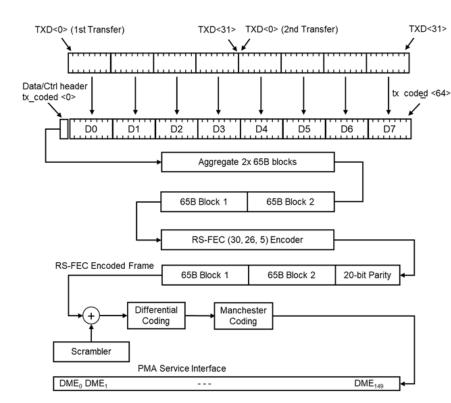

## Low data framing data mode

- Symbol rate is 117.1875 MHz

- Differential Manchester encoding

- Correction of impulse noise errors lasting from 51ns (6 bits) to 85ns (10 bits).

- Decoding latency of approximately1.5 us

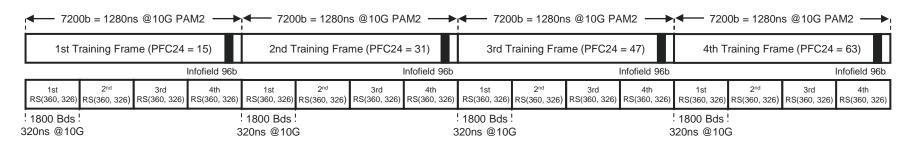

## LDR vs 10G training frame

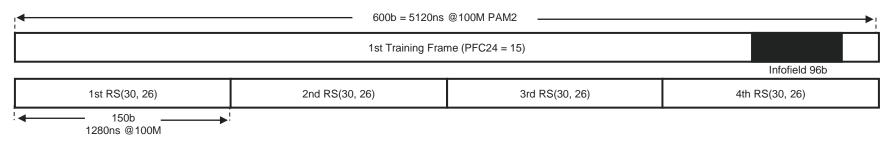

#### 10G Training Frame

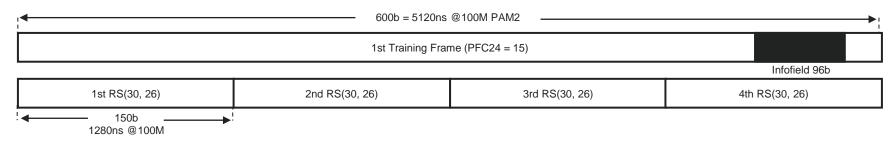

#### 100M Training Frame

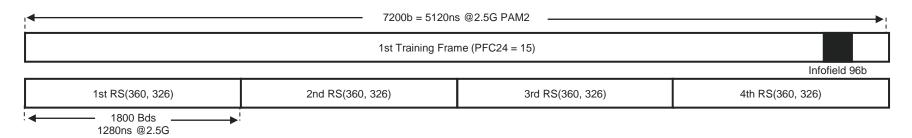

## LDR vs 5G training frame

#### **5G Training Frame**

### 100M Training Frame

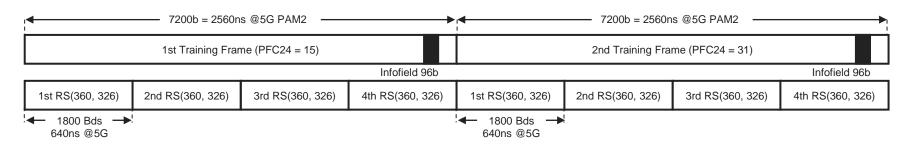

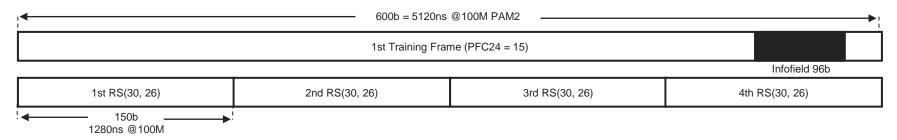

## LDR vs 2.5G training frame

#### 2.5G Training Frame

#### 100M Training Frame

### Conclusion

- High data rate (HDR) path framing matches the 802.3ch specification

- Low data rate path framing

- FEC Latency = 1.5 us

- 17% overhead

- Burst error correction 51-85ns

- No OAM from switch to camera

- The training frame in low data rate path is

- independent of speed of HDR path

- Aligned with framing of HDR path

- We welcome collaboration on framing in both data mode and training